ADSP-21992(RevPrA) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-21992 Datasheet PDF : 48 Pages

| |||

PRELIMINARY TECHNICAL DATA

August 2002

For current information contact Analog Devices at (781) 937-1799

ADSP-21992

signal can be programmed to set the FLAG on either a level

(level sensitive input/interrupt) or an edge (edge sensitive

input/interrupt).

The FIO module can also be used to generate an asynchro-

nous unregistered wake up signal FIO_WAKEUP for DSP

core wake up after power down.

The FIO Lines, PF7 - PF1 can also be configured as external

slave select outputs for the SPI Communications Port, while

PF0 can be configured to act as a Slave select input.

The FIO Lines can be configured to act as a PWM shutdown

source for the three phase PWM generation unit of the

ADSP-21992.

Watchdog Timer

The ADSP-21992 integrates a watchdog timer that can be

used as a protection mechanism against unintentional

software events. It can be used to cause a complete DSP and

peripheral reset in such an event. The watchdog timer

consists of a 16-bit timer that is clocked at the external clock

rate (CLKIN or crystal input frequency).

In order to prevent an unwanted timeout or reset, it is

necessary to periodically write to the watchdog timer

register. During abnormal system operation, the watchdog

count will eventually decrement to 0 and a watchdog

timeout will occur. In the system, the watchdog timeout will

cause a full reset of the DSP core and peripherals.

General Purpose Timers

The ADSP-21992 contains a general purpose timer unit

that contains three identical 32-bit timers. The three pro-

grammable interval timers (Timer0, Timer1 and Timer2)

generate periodic interrupts. Each timer can be indepen-

dently set to operate in one of three modes:

• Pulse Waveform Generation (PWM_OUT) mode

• Pulse Width Count/Capture (WDTH_CAP) mode

• External Event Watchdog (EXT_CLK) mode

Each Timer has one bidirectional chip pin, TMR2-TMR0.

For each timer, the associated pin is configured as an output

pin in PWM_OUT Mode and as input pin in WDTH_CAP

and EXT_CLK Modes.

Interrupts

The interrupt controller lets the DSP respond to 17 inter-

rupts with minimum overhead. The DSP core implements

an interrupt priority scheme as shown in Table 2. Applica-

tions can use the unassigned slots for software and

peripheral interrupts. The Peripheral Interrupt Controller

is used to assign the various peripheral interrupts to the 12

user assignable interrupts of the DSP core.

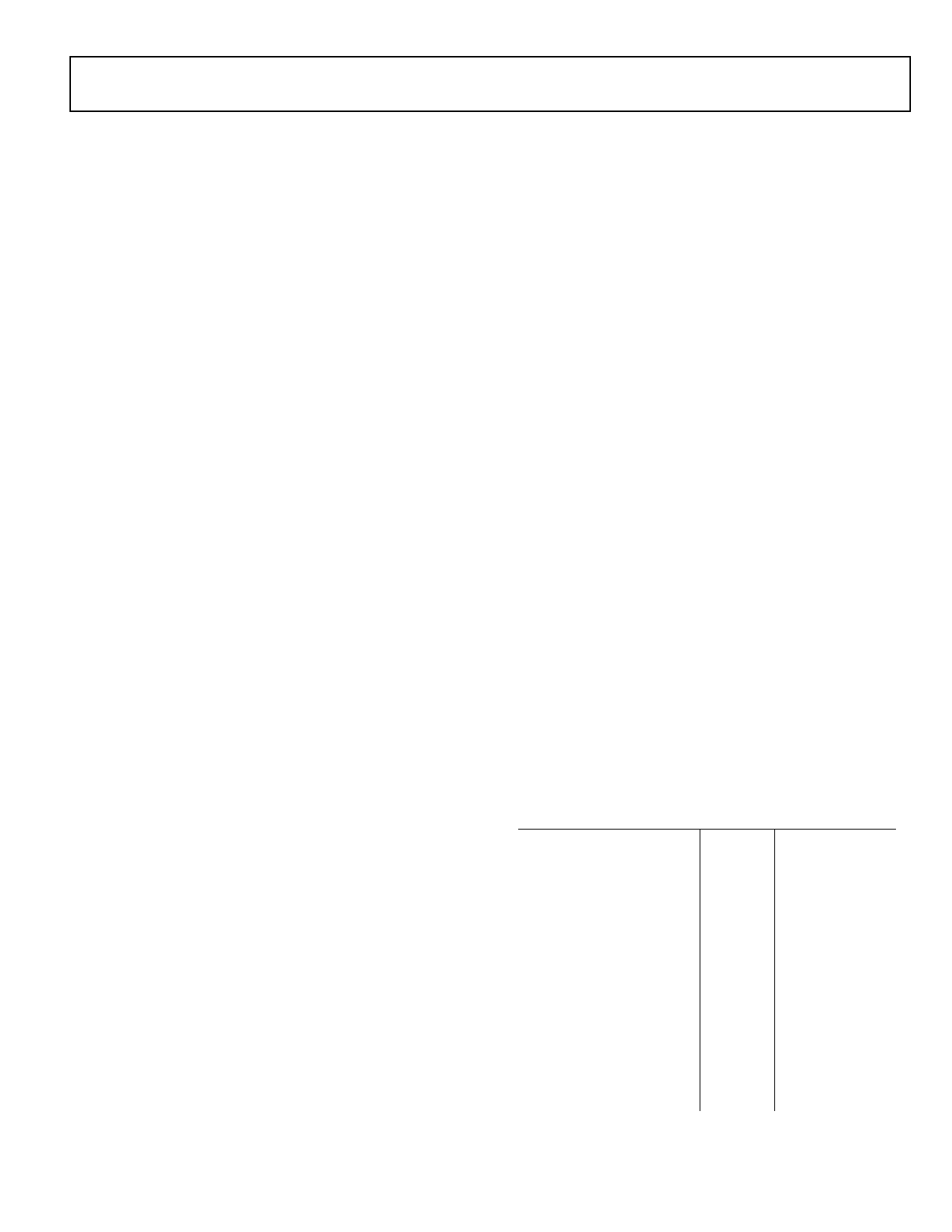

Table 2. Interrupt Priorities/Addresses

Interrupt

Emulator (NMI)

—Highest Priority

Reset (NMI)

Power Down (NMI)

Loop and PC Stack

Emulation Kernel

User Assigned Interrupt

(USR0)

User Assigned Interrupt

(USR1)

User Assigned Interrupt

(USR2)

User Assigned Interrupt

(USR3)

User Assigned Interrupt

(USR4)

User Assigned Interrupt

(USR5)

User Assigned Interrupt

(USR6)

User Assigned Interrupt

(USR7)

User Assigned Interrupt

(USR8)

User Assigned Interrupt

(USR9)

User Assigned Interrupt

(USR10)

User Assigned Interrupt

(USR11)

—Lowest Priority

IMASK/

IRPTL

NA

Vector Address

NA

0

0x00 0000

1

0x00 0020

2

0x00 0040

3

0x00 0060

4

0x00 0080

5

0x00 00A0

6

0x00 00C0

7

0x00 00E0

8

0x00 0100

9

0x00 0120

10

0x00 0140

11

0x00 0160

12

0x00 0180

13

0x00 01A0

14

0x00 01C0

15

0x00 01E0

There is no assigned priority for the peripheral interrupts

after reset. To assign the peripheral interrupts a different

priority, applications write the new priority to their corre-

sponding control bits (determined by their ID) in the

Interrupt Priority Control register.

Interrupt routines can either be nested with higher priority

interrupts taking precedence or processed sequentially.

Interrupts can be masked or unmasked with the IMASK

register. Individual interrupt requests are logically ANDed

with the bits in IMASK; the highest priority unmasked

interrupt is then selected. The emulation, power down, and

reset interrupts are nonmaskable with the IMASK register,

but software can use the DIS INT instruction to mask the

power down interrupt.

REV. PrA This information applies to a product under development Its characteristics and specifications are subject to change without notice Analog

11

Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing