TE28F400B3T110 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

TE28F400B3T110 Datasheet PDF : 48 Pages

| |||

SMART 3 ADVANCED BOOT BLOCK

E

3.3 Block Locking

The Smart 3 Advanced Boot Block flash memory

architecture features two hardware-lockable

parameter blocks.

3.3.1

WP# = VIL FOR BLOCK LOCKING

The lockable blocks are locked when WP# = VIL;

any program or erase operation to a locked block

will result in an error, which will be reflected in the

status register. For top configuration, the top two

parameter blocks (blocks #69 and #70, blocks #37

and #38 for the 16-Mbit, blocks #21 and #22 for the

8-Mbit, blocks #13 and #14 for the 4-Mbit) are

lockable. For the bottom configuration, the bottom

two parameter blocks (blocks #0 and #1 for 4-/8-/

16-/32-Mbit) are lockable. Unlocked blocks can be

programmed or erased normally (unless VPP is

below VPPLK).

3.3.2

WP# = VIH FOR BLOCK UNLOCKING

WP# = VIH unlocks all lockable blocks.

These blocks can now be programmed or erased.

Note that RP# does not override WP# locking as in

previous Boot Block devices. WP# controls all block

locking and VPP provides protection against

spurious writes. Table 8 defines the write protection

methods.

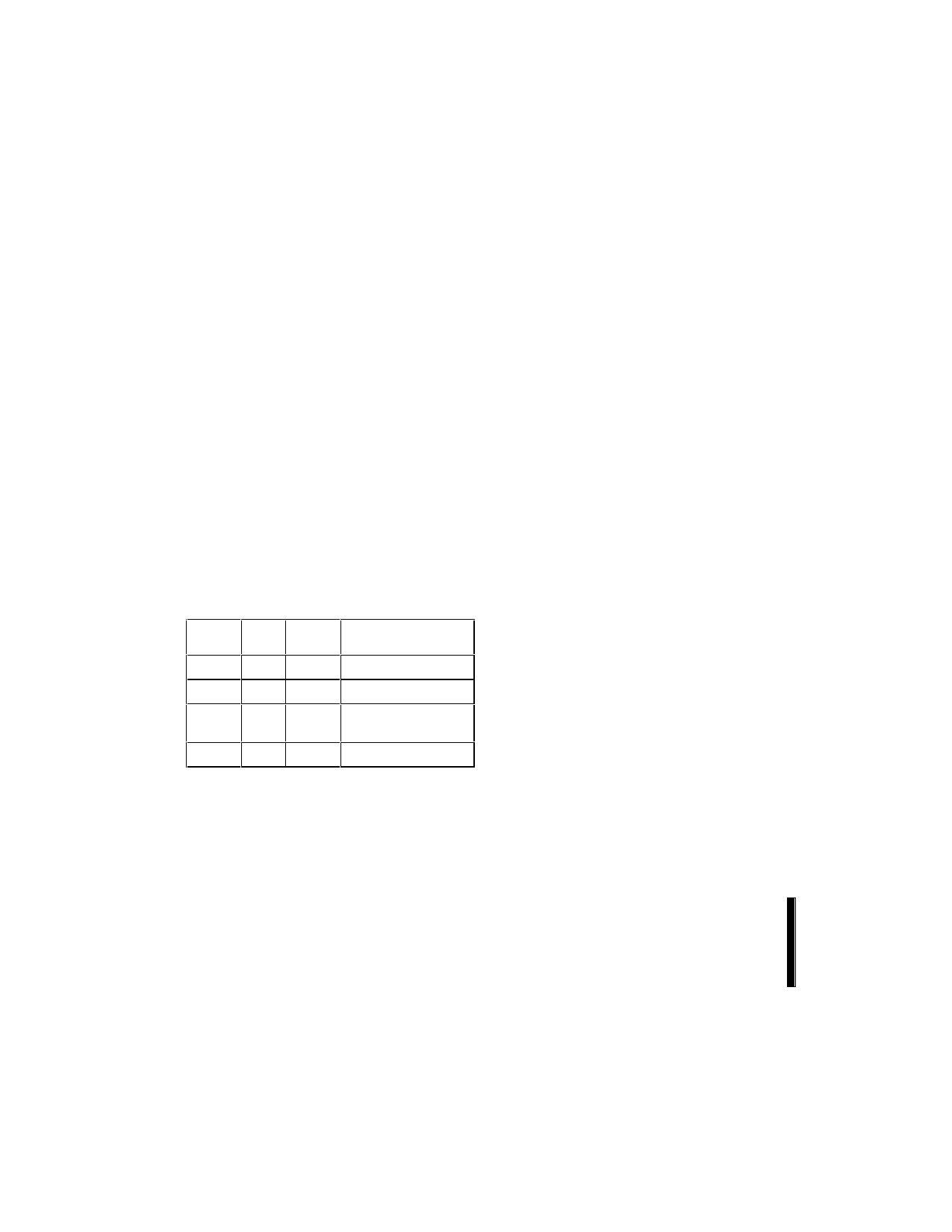

Table 8. Write Protection Truth Table for

Advanced Boot Block Flash Memory Family

VPP WP# RP#

Write Protection

Provided

X

X

VIL

VIL

X

VIH

≥ VPPLK VIL

VIH

All Blocks Locked

All Blocks Locked

Lockable Blocks

Locked

≥ VPPLK VIH

VIH

All Blocks Unlocked

3.4 VPP Program and Erase

Voltages

Intel’s Smart 3 products provide in-system

programming and erase at 2.7 V. For customers

requiring fast programming in their manufacturing

environment, Smart 3 includes an additional low-

cost 12 V programming feature.

The 12 V VPP mode enhances programming

performance during the short period of time typically

found in manufacturing processes; however, it is

not intended for extended use. 12 V may be applied

to VPP during program and erase operations for a

maximum of 1000 cycles on the main blocks and

2500 cycles on the parameter blocks. VPP may be

connected to 12 V for a total of 80 hours maximum.

Stressing the device beyond these limits may cause

permanent damage.

During read operations or idle times, VPP may be

tied to a 5 V supply. For program and erase

operations, a 5 V supply is not permitted. The VPP

must be supplied with either 2.7 V–3.6 V or 11.4 V–

12.6 V during program and erase operations.

3.4.1

VPP = VIL FOR COMPLETE

PROTECTION

The VPP programming voltage can be held low for

complete write protection of all blocks in the flash

device. When VPP is below VPPLK, any program or

erase operation will result in a error, prompting the

corresponding status register bit (SR.3) to be set.

3.5 Power Consumption

Intel® Flash devices have a tiered approach to

power savings that can significantly reduce overall

system power consumption. The Automatic Power

Savings (APS) feature reduces power consumption

when the device is selected but idle. If the CE# is

deasserted, the flash enters its standby mode,

where current consumption is even lower. The

combination of these features can minimize

memory power consumption, and therefore, overall

system power consumption.

20

PRELIMINARY