ISL12023 Ver la hoja de datos (PDF) - Renesas Electronics

NГәmero de pieza

componentes DescripciГіn

Fabricante

ISL12023

ISL12023 Datasheet PDF : 29 Pages

| |||

ISL12023

Register Descriptions

The battery-backed registers are accessible following a slave

byte of вҖң1101111xвҖқ and reads or writes to addresses [00h:2Fh].

The defined addresses and default values are described in the

Table 1. The battery backed general purpose SRAM has a

different slave address (1010111x), so it is not possible to

read/write that section of memory while accessing the registers.

REGISTER ACCESS

The contents of the registers can be modified by performing a

byte or a page write operation directly to any register address.

The registers are divided into 8 sections. They are:

1. Real Time Clock (7 bytes): Address 00h to 06h.

2. Control and Status (13 bytes): Address 07h to 0Fh and 2Ah to

2Dh.

3. Alarm (6 bytes): Address 10h to 15h.

4. Time Stamp for Battery Status (5 bytes): Address 16h to 1Ah.

5. Time Stamp for VDD Status (5 bytes): Address 1Bh to 1Fh.

6. Daylight Saving Time (8 bytes): 20h to 27h.

7. Temperature (2 bytes): 28h to 29h

8. Crystal Net PPM Correction, NPPM (2 bytes): 2Ah, 2Bh

9. Crystal Turnover Temperature, XT0 (1 byte): 2Ch

10. Crystal ALPHA at high temperature, ALPHA_H (1 byte): 2Dh

11. Scratch Pad (2 bytes): Address 2Eh and 2Fh

Write capability is allowable into the RTC registers (00h to 06h)

only when the WRTC bit (bit 6 of address 08h) is set to вҖң1вҖқ. A

multi-byte read or write operation should be limited to one

section per operation for best RTC time keeping performance.

When the previous address is 2Fh, the next address will wrap

around to 00h.

A register can be read by performing a random read at any

address at any time. This returns the contents of that register

location. Additional registers are read by performing a sequential

read. For the RTC and Alarm registers, the read instruction

latches all clock registers into a buffer, so an update of the clock

does not change the time being read. At the end of a read, the

master supplies a stop condition to end the operation and free

the bus. After a read, the address remains at the previous

address +1 so the user can execute a current address read and

continue reading the next register.

It is not necessary to set the WRTC bit prior to writing into the

control and status, alarm, and user SRAM registers.

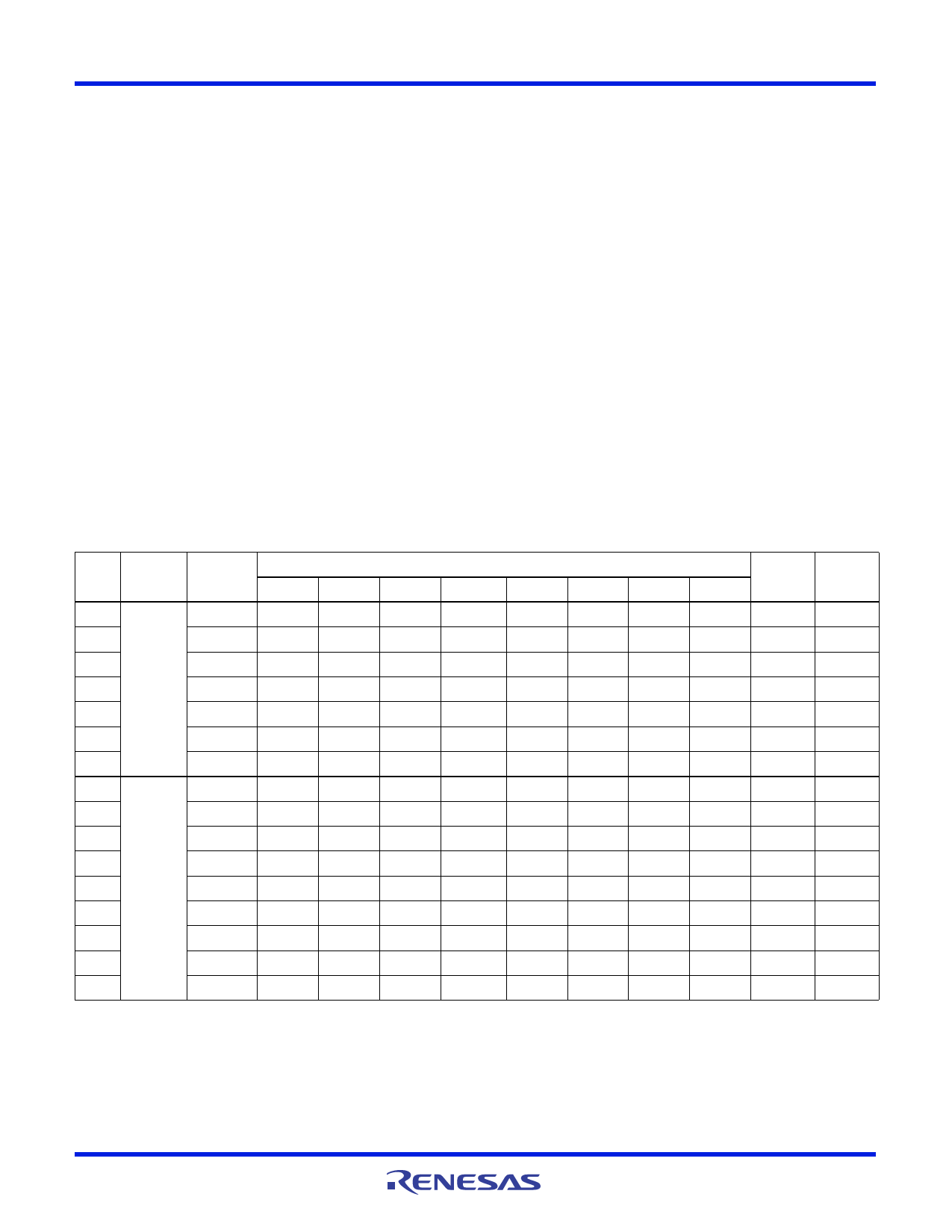

TABLE 1. REGISTER MEMORY MAP

ADDR. SECTION

00h

RTC

REG

NAME

SC

BIT

7

6

5

4

3

2

1

0

RANGE DEFAULT

0

SC22 SC21

SC20

SC13 SC12 SC11 SC10 0 to 59

00h

01h

MN

0

MN22 MN21 MN20 MN13 MN12 MN11 MN10 0 to 59

00h

02h

HR

MIL

0

HR21

HR20 HR13 HR12 HR11 HR10 0 to 23

00h

03h

DT

0

0

DT21

DT20

DT13

DT12

DT11

DT10 1 to 31

01h

04h

MO

0

0

0

MO20 MO13 MO12 MO11 MO10 1 to 12

01h

05h

YR

YR23 YR22 YR21

YR20

YR13 YR12 YR11 YR10 0 to 99

00h

06h

DW

0

0

0

0

0

DW2

DW1

DW0

0 to 6

00h

07h

CSR

SR

BUSY OSCF DSTADJ ALM

LVDD LBAT85 LBAT75 RTCF

N/A

01h

08h

INT

ARST WRTC

IM

FOBATB FO3

FO2

FO1

FO0

N/A

01h

09h

PWR_VDD CLRTS

D

D

D

D

VDDTrip2 VDDTrip1 VDDTrip0 N/A

00h

0Ah

PWR_VBAT

RESEALB VB85Tp2 VB85Tp1 VB85Tp0 VB75Tp2 VB75Tp1 VB75Tp0 N/A

00h

0Bh

ITRO

IDTR01 IDTR00 IATR05 IATR04 IATR03 IATR02 IATR01 IATR00

N/A

20h

0Ch

ALPHA

D

ALPHA6 ALPHA5 ALPHA4 ALPHA3 ALPHA2 ALPHA1 ALPHA0 N/A

46h

0Dh

BETA

TSE

BTSE

BTSR BETA4 BETA3 BETA2 BETA1 BETA0

N/A

00h

0Eh

FATR

0

0

FFATR5 FATR4 FATR3 FATR2 FATR1 FATR0

N/A

00h

0Fh

FDTR

0

0

0

FDTR4 FDTR3 FDTR2 FDTR1 FDTR0

N/A

00h

FN6682 Rev 3.00

December 6, 2011

Page 11 of 29