AD9250(Rev0) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

AD9250

(Rev.:Rev0)

(Rev.:Rev0)

AD9250 Datasheet PDF : 44 Pages

| |||

Data Sheet

AD9250

CLOCK INPUT

0.1µF

CLOCK INPUT

0.1µF

VDD

127Ω

127Ω

0.1µF

AD9515

LVPECL

DRIVER

0.1µF

82.5Ω

82.5Ω

ADC

50Ω Tx LINE

0.1µF

50Ω

RFCLK

Figure 46. Differential PECL RF Clock Input Circuit

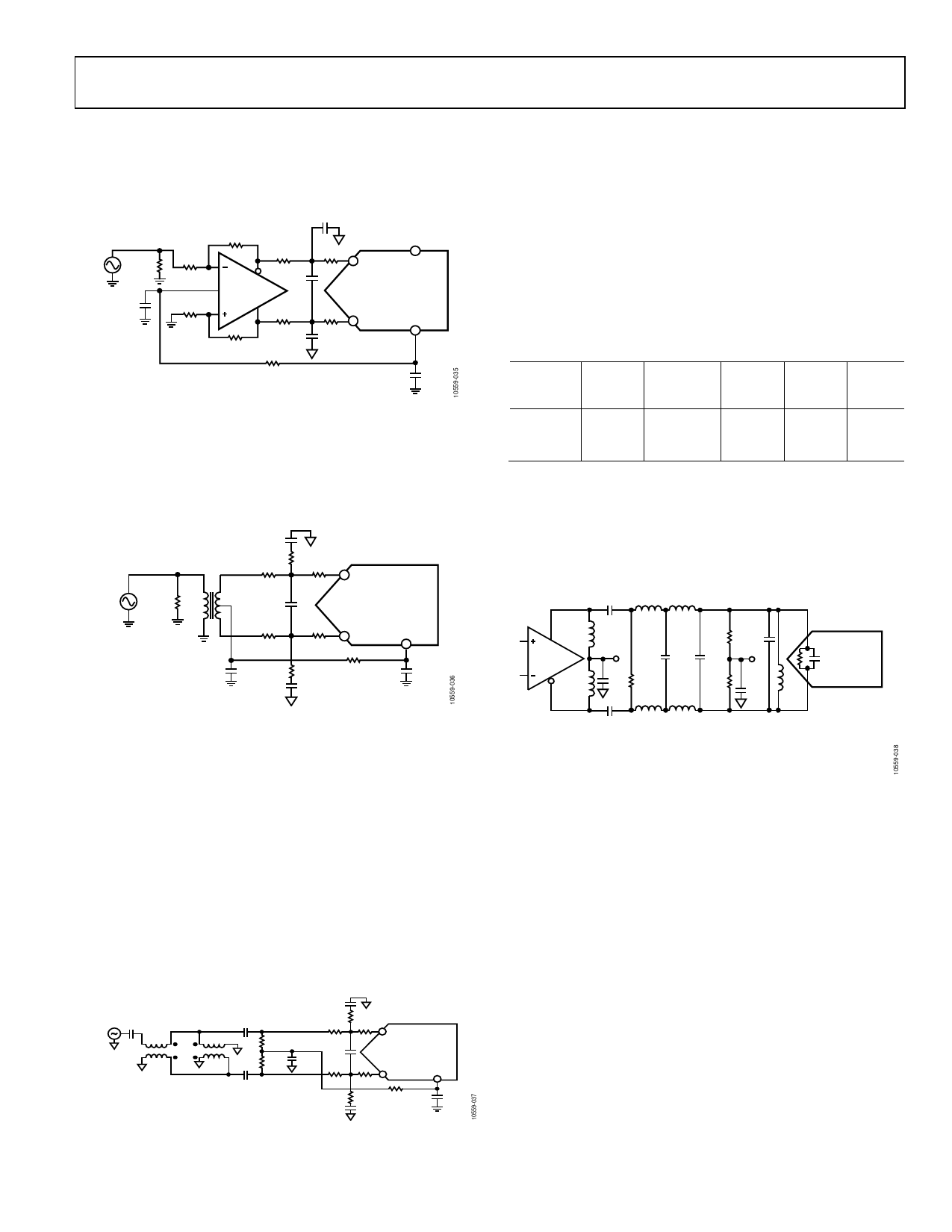

Figure 46 shows the RF clock input of the AD9250 being driven

from the LVPECL outputs of the AD9515. The differential

LVPECL output signal from the AD9515 is converted to a single-

ended signal using an RF balun or RF transformer. The RF balun

configuration is recommended for clock frequencies associated

with the RF clock input.

Input Clock Divider

The AD9250 contains an input clock divider with the ability to

divide the Nyquist input clock by integer values between 1 and 8.

The RF clock input uses an on-chip predivider to divide the clock

input by four before it reaches the 1 to 8 divider. This allows

higher input frequencies to be achieved on the RF clock input. The

divide ratios can be selected using Register 0x09 and Register 0x0B.

Register 0x09 is used to set the RF clock input, and Register 0x0B

can be used to set the divide ratio of the 1-to-8 divider for both

the RF clock input and the Nyquist clock input. For divide ratios

other than 1, the duty-cycle stabilizer is automatically enabled.

RFCLK

÷4

NYQUIST

CLOCK

÷1 TO ÷8

DIVIDER

Figure 47. AD9250 Clock Divider Circuit

The AD9250 clock divider can be synchronized using the external

SYSREF input. Bit 1 and Bit 2 of Register 0x3A allow the clock

divider to be resynchronized on every SYSREF signal or only on

the first signal after the register is written. A valid SYSREF causes

the clock divider to reset to its initial state. This synchronization

feature allows multiple parts to have their clock dividers aligned to

guarantee simultaneous input sampling.

Clock Duty Cycle

Jitter on the rising edge of the input clock is still of paramount

concern and is not reduced by the duty cycle stabilizer. The duty

cycle control loop does not function for clock rates less than

40 MHz nominally. The loop has a time constant associated

with it that must be considered when the clock rate can change

dynamically. A wait time of 1.5 µs to 5 µs is required after a

dynamic clock frequency increase or decrease before the DCS

loop is relocked to the input signal. During the time that the

loop is not locked, the DCS loop is bypassed, and the internal

device timing is dependent on the duty cycle of the input clock

signal. In such applications, it may be appropriate to disable the

duty cycle stabilizer. In all other applications, enabling the DCS

circuit is recommended to maximize ac performance.

Jitter Considerations

High speed, high resolution ADCs are sensitive to the quality of

the clock input. The degradation in SNR at a given input frequency

(fIN) due to jitter (tJ) can be calculated by

SNRHF = −10 log[(2π × fIN × tJRMS)2 + 10 (−SNRLF /10) ]

In the equation, the rms aperture jitter represents the root-mean-

square of all jitter sources, which include the clock input, the

analog input signal, and the ADC aperture jitter specification. IF

undersampling applications are particularly sensitive to jitter,

as shown in Figure 48.

80

75

70

65

Typical high speed ADCs use both clock edges to generate a

variety of internal timing signals and, as a result, may be sensitive to

clock duty cycle. Commonly, a ±5% tolerance is required on the

clock duty cycle to maintain dynamic performance characteristics.

The AD9250 contains a DCS that retimes the nonsampling (falling)

edge, providing an internal clock signal with a nominal 50% duty

cycle. This allows the user to provide a wide range of clock input

duty cycles without affecting the performance of the AD9250.

60

0.05ps

0.2ps

0.5ps

55

1ps

1.5ps

MEASURED

50

1

10

100

INPUT FREQUENCY (MHz)

1000

Figure 48. AD9250-250 SNR vs. Input Frequency and Jitter

Rev. 0 | Page 21 of 44