GT28F400B3B150 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

GT28F400B3B150 Datasheet PDF : 49 Pages

| |||

SMART 3 ADVANCED BOOT BLOCK–WORD-WIDE

E

3.0 PRINCIPLES OF OPERATION

Flash memory combines EEPROM functionality

with in-circuit electrical program and erase

capability. The Smart 3 Advanced Boot Block flash

memory family utilizes a Command User Interface

(CUI) and automated algorithms to simplify program

and erase operations. The CUI allows for 100%

CMOS-level control inputs, fixed power supplies

during erasure and programming, and maximum

EEPROM compatibility.

When VPP < VPPLK, the device will only execute the

following commands successfully: Read Array,

Read Status Register, Clear Status Register and

Read Intelligent Identifier. The device provides

standard EEPROM read, standby and output

disable operations. Manufacturer identification and

device identification data can be accessed through

the CUI. In addition, 2.7V or 12V on VPP allows

program and erase of the device. All functions

associated with altering memory contents, namely

program and erase, are accessible via the CUI.

The internal Write State Machine (WSM) completely

automates program and erase operations while the

CUI signals the start of an operation and the status

register reports status. The CUI handles the WE#

interface to the data and address latches, as well

as system status requests during WSM operation.

3.1 Bus Operation

Smart 3 Advanced Boot Block flash memory

devices read, program and erase in-system via the

local CPU or microcontroller. All bus cycles to or

from the flash memory conform to standard

microcontroller bus cycles. Four control pins dictate

the data flow in and out of the flash component:

CE#, OE#, WE# and RP#. These bus operations

are summarized in Table 3.

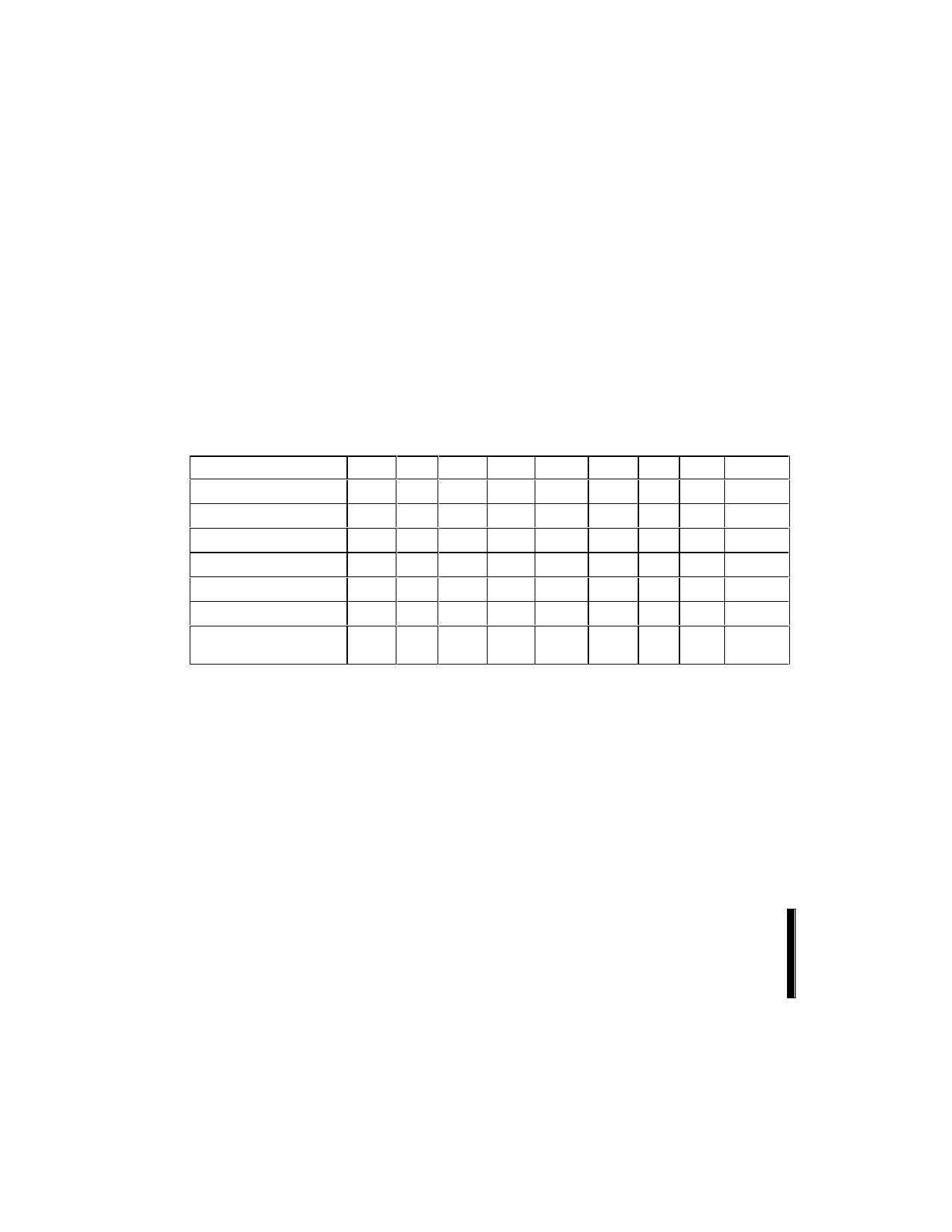

Table 3. Bus Operations for Word-Wide Mode

Mode

Notes RP# CE# OE# WE# WP# A0

Read

1,2,3 VIH

VIL

VIL

VIH

X

X

Output Disable

2

VIH

VIL

VIH

VIH

X

X

Standby

2

VIH

VIH

X

X

X

X

Deep Power-Down

2,9

VIL

X

X

X

X

X

Intelligent Identifier (Mfr.) 2,4 VIH VIL

VIL

VIH

X

VIL

Intelligent Identifier (Dvc.) 2,4,5 VIH VIL

VIL

VIH

X

VIH

Write

2,6,7, VIH

VIL

VIH

VIL

8

X

X

NOTES:

1. Refer to DC Characteristics.

2. X must be VIL, VIH for control pins and addresses, VPPLK , VPPH1 or VPPH2 for VPP.

3. See DC Characteristics for VPPLK, VPPH1, VPPH2 voltages.

4. Manufacturer and device codes may also be accessed via a CUI write sequence, A1–A19 = X

5. See Table 5 for device IDs.

6. Refer to Table 6 for valid DIN during a write operation.

7. Command writes for block erase or word program are only executed when VPP = VPPH1 or VPPH2.

8. To program or erase the lockable blocks, hold WP# at VIH. See Section 3.3.

9. RP# must be at GND ± 0.2V to meet the maximum deep power-down current specified.

VPP

DQ0–15

X

DOUT

X

High Z

X

High Z

X

High Z

X 0089 H

X

See Table 5

VPPH

DIN

14

PRELIMINARY