28F008C3 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

28F008C3 Datasheet PDF : 59 Pages

| |||

E

3 VOLT ADVANCED+ BOOT BLOCK

3.0 PRINCIPLES OF OPERATION

The 3 Volt Advanced+ Boot Block flash memory

family utilizes a CUI and automated algorithms to

simplify program and erase operations. The CUI

allows for 100% CMOS-level control inputs and

fixed power supplies during erasure and

programming.

The internal WSM completely automates program

and erase operations while the CUI signals the start

of an operation and the status register reports

status. The CUI handles the WE# interface to the

data and address latches, as well as system status

requests during WSM operation.

the VPP voltage. The appropriate read mode

command must be issued to the CUI to enter the

corresponding mode. Upon initial device power-up

or after exit from reset, the device automatically

defaults to read array mode.

CE# and OE# must be driven active to obtain data

at the outputs. CE# is the device selection control;

when active it enables the flash memory device.

OE# is the data output control and it drives the

selected memory data onto the I/O bus. For all read

modes, WE# and RP# must be at VIH. Figure 9

illustrates a read cycle.

3.1.2

OUTPUT DISABLE

3.1 Bus Operation

The 3 Volt Advanced+ Boot Block flash memory

devices read, program and erase in-system via the

local CPU or microcontroller. All bus cycles to or

from the flash memory conform to standard

microcontroller bus cycles. Four control pins dictate

the data flow in and out of the flash component:

CE#, OE#, WE# and RP#. These bus operations

are summarized in Table 3.

3.1.1

READ

The flash memory has four read modes available:

read array, read configuration, read status and read

query. These modes are accessible independent of

With OE# at a logic-high level (VIH), the device

outputs are disabled. Output pins are placed in a

high-impedance state.

3.1.3

STANDBY

Deselecting the device by bringing CE# to a logic-

high level (VIH) places the device in standby mode,

which substantially reduces device power

consumption without any latency for subsequent

read accesses. In standby, outputs are placed in a

high-impedance state independent of OE#. If

deselected during program or erase operation, the

device continues to consume active power until the

program or erase operation is complete.

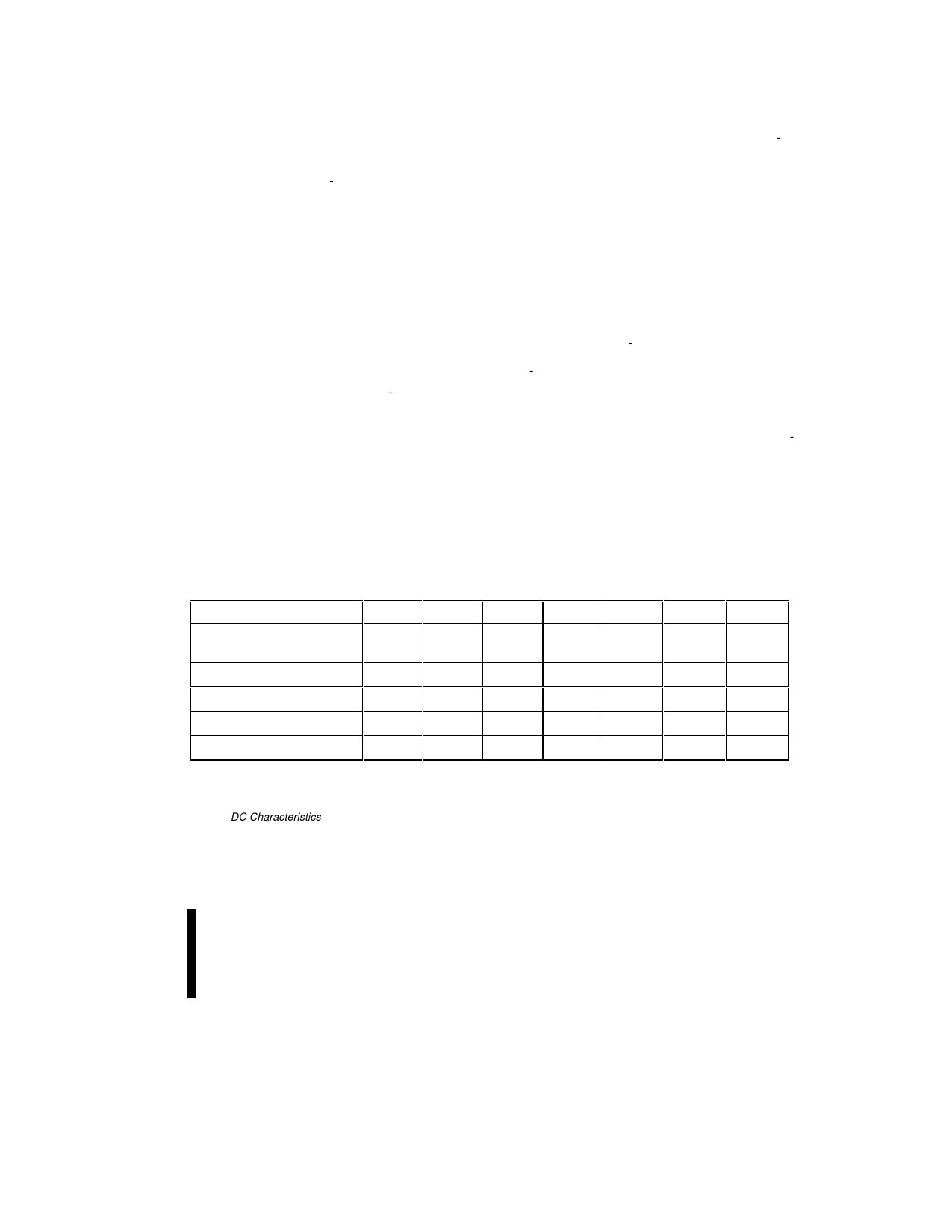

Table 3. Bus Operations(1)

Mode

Read (Array, Status,

Configuration, or Query)

Note

2-4

RP#

VIH

CE#

VIL

OE#

VIL

WE#

VIH

DQ0–7

DOUT

DQ8-15

DOUT

Output Disable

2

VIH

VIL

VIH

VIH

High Z High Z

Standby

2

VIH

VIH

X

X

High Z High Z

Reset

2,7

VIL

X

X

X

High Z High Z

Write

2,5-7

VIH

VIL

VIH

VIL

DIN

DIN

NOTES:

1. 8-bit devices use only DQ[0:7], 16-bit devices use DQ[0:15]

2. X must be VIL, VIH for control pins and addresses.

3. See DC Characteristics for VPPLK, VPP1, VPP2, VPP3, voltages.

4. Manufacturer and device codes may also be accessed in read configuration mode (A1–A20 = 0). See Table 4.

5. Refer to Table 5 for valid DIN during a write operation.

6. To program or erase the lockable blocks, hold WP# at VIH.

7. RP# must be at GND ± 0.2 V to meet the maximum deep power-down current specified.

PRODUCT PREVIEW

11