28F008C3 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

28F008C3 Datasheet PDF : 59 Pages

| |||

3 VOLT ADVANCED+ BOOT BLOCK

E

3.3.5

READING A BLOCK’S LOCK STATUS

The lock status of every block can be read in the

Configuration Read mode of the device. To enter

this mode, write 90H to the device. Subsequent

reads at Block Address + 00002 will output the lock

status of that block. The lock status is represented

by the lowest two output pins, DQ0 and DQ1. DQ0

indicates the Block Lock/Unlock status and is set by

the Lock command and cleared by the Unlock

command. It is also automatically set when entering

Lock-Down. DQ1 indicates Lock-Down status and is

set by the Lock-Down command. It cannot be

cleared by software, only by device reset or power-

down.

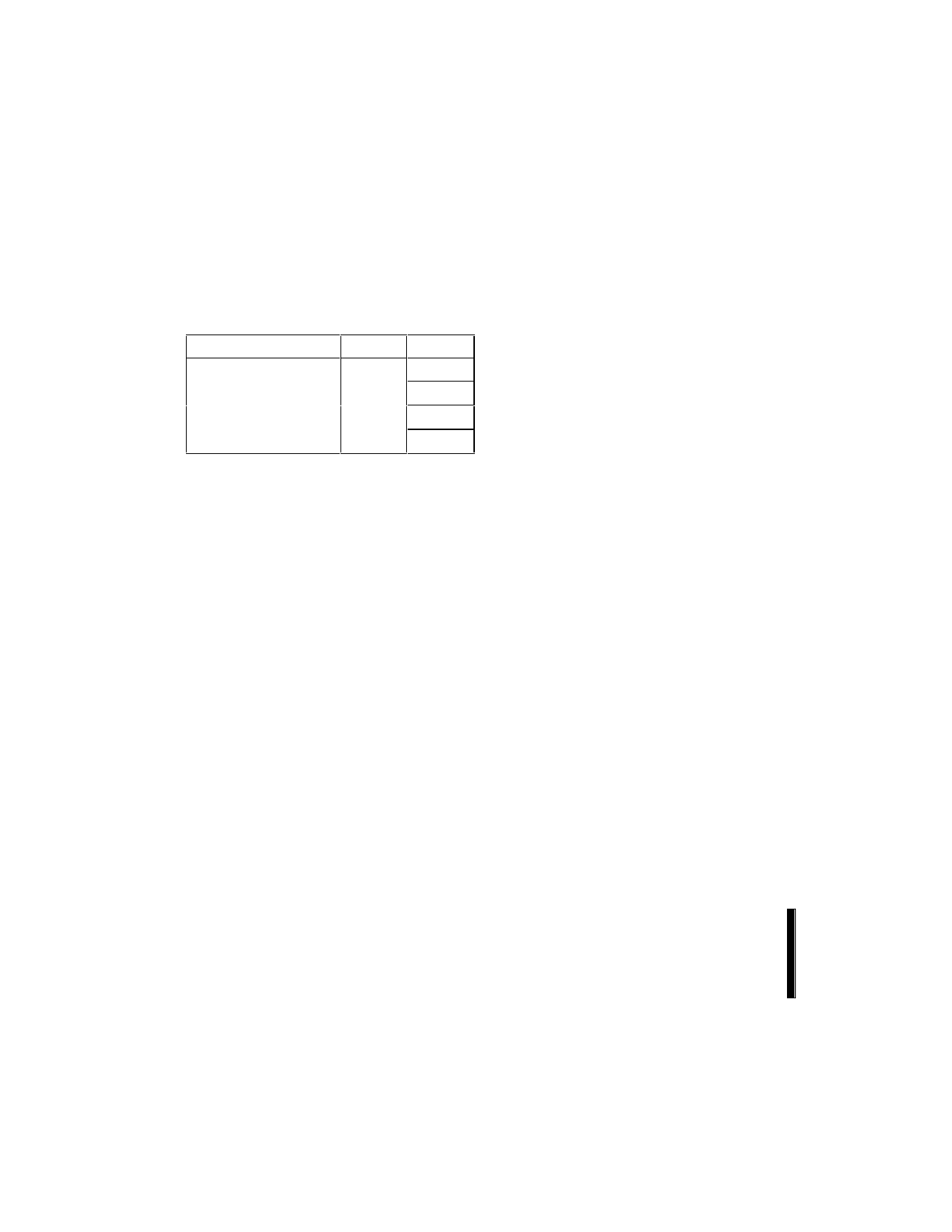

Table 8. Block Lock Status

Item

Address Data

Block Lock Configuration XX002 LOCK

• Block Is Unlocked

• Block Is Locked

DQ0 = 0

DQ0 = 1

• Block Is Locked-Down

DQ1 = 1

3.3.6

LOCKING OPERATIONS DURING

ERASE SUSPEND

Changes to block lock status can be performed

during an erase suspend by using the standard

locking command sequences to unlock, lock, or

lock-down a block. This is useful in the case when

another block needs to be updated while an erase

operation is in progress.

To change block locking during an erase operation,

first write the erase suspend command (B0H), then

check the status register until it indicates that the

erase operation has been suspended. Next write

the desired lock command sequence to a block and

the lock status will be changed. After completing

any desired lock, read, or program operations,

resume the erase operation with the Erase Resume

command (D0H).

If a block is locked or locked-down during a

suspended erase of the same block, the locking

status bits will be changed immediately, but when

the erase is resumed, the erase operation will

complete.

Locking operations cannot be performed during a

program suspend. Refer to Appendix A for detailed

information on which commands are valid during

erase suspend.

3.3.7

STATUS REGISTER ERROR

CHECKING

Using nested locking or program command

sequences during erase suspend can introduce

ambiguity into status register results.

Since locking changes are performed using a two

cycle command sequence, e.g., 60H followed by

01H to lock a block, following the Configuration

Setup command (60H) with an invalid command will

produce a lock command error (SR.4 and SR.5 will

be set to 1) in the status register. If a lock

command error occurs during an erase suspend,

SR.4 and SR.5 will be set to 1, and will remain at 1

after the erase is resumed. When erase is

complete, any possible error during the erase

cannot be detected via the status register because

of the previous locking command error.

A similar situation happens if an error occurs during

a program operation error nested within an erase

suspend.

20

PRODUCT PREVIEW