UT1750AR12WCC Ver la hoja de datos (PDF) - Aeroflex UTMC

Número de pieza

componentes Descripción

Fabricante

UT1750AR12WCC Datasheet PDF : 56 Pages

| |||

The UT1750AR loads the eight bits of serial data into the lower

eight bits of the TXMT (figure 13).

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TT TTTTTT

D D DDDDD DXX XXXXXX

C C C C C C C C D D D D DD D D

76 5 4 32 10

MSB

DC = Don’t Care

LSB

Figure 13. The UART Transmitter

The Pending Interrupt Register (PI)

The Pending Interrupt Register (PI) contains information on

pending interrupts attempting to vector the Instruction Counter

Register (IC) to a new location. Software or hardware controls

the PI. Any system interrupt, when active, sets the

corresponding bit in the PI. RISC I/O instructions can also set,

clear, and read the PI (figure 14).

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PM I FFEF T I T I I I I I I

W C N L I X L I N I N NONON

D H T P PCP MTM T T LT LT

N E OOOLU A 1B 2 3 1 4 2 5

MSB

LSB

Figure 14. The Pending Interrupt Register (PI)

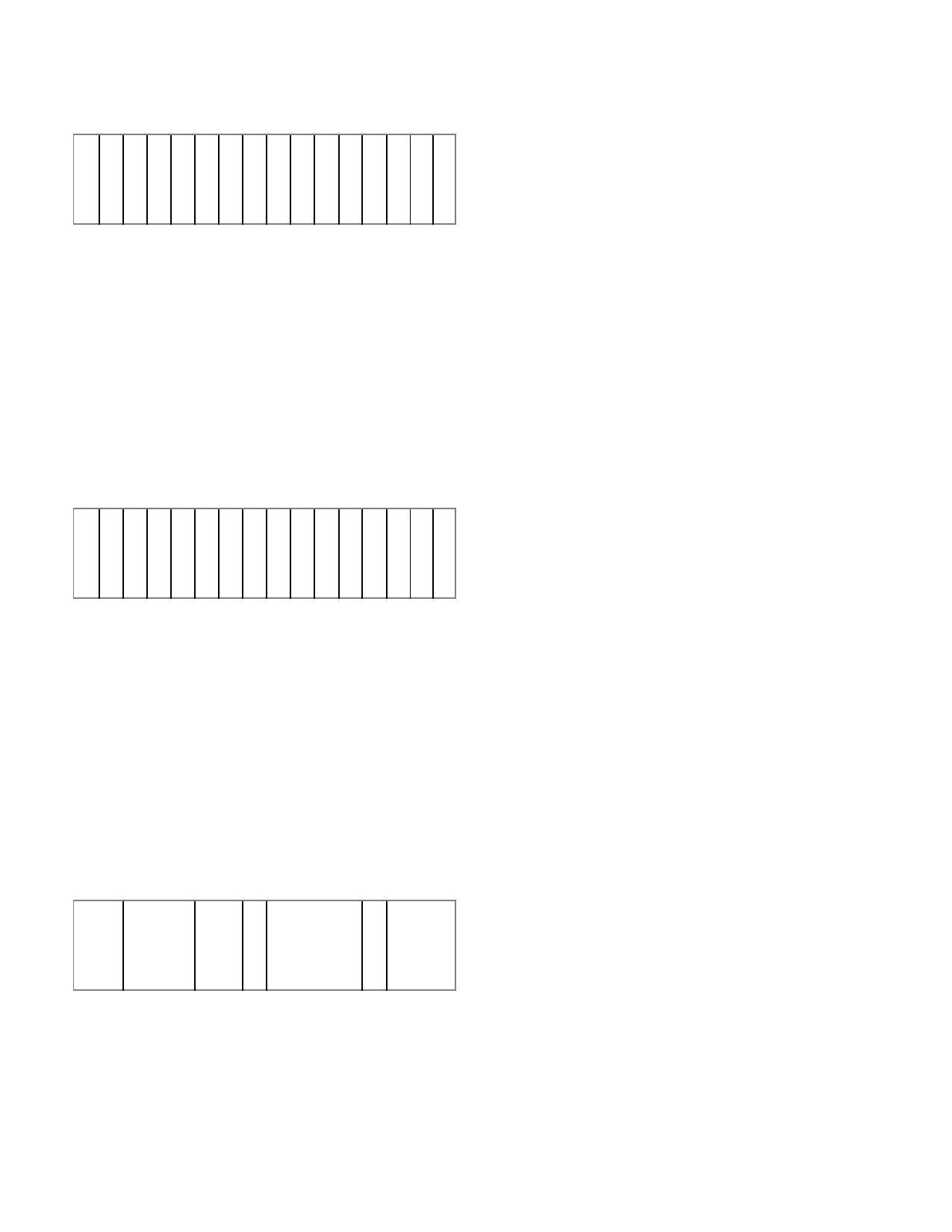

The Fault Register (FT)

The UT1750AR uses the Fault Register (FT) (figure 15) to

indicate the occurrence of a machine-error fault. A machine-

error fault cannot be disabled. The UT1750AR uses the logical

OR combination of the 16 FT bits to generate the Machine Error

interrupt, bit 14 of the PI. Any bits in the FT the UT1750AR

does not use are set to a logic zero. The UT1750AR reads, loads,

and clears the FT with RISC I/O instructions. The configuration

of the FT is shown in figure 15.

15 14 13 12 11 10 9

MEM PARITY I/O

PROT

876 54 3

S ILLEGAL R

Y

INSTRUC-

TION AND

E

F ADD FAULT S

T

2 10

BUILT-

IN-

TEST

MSB

Figure 15. The Fault Register (FT)

LSB

Bit Definitions

All bits in the Fault Register are active when high.

BIT

NUMBER MNEMONIC

DESCRIPTION

15

CMPF

CPU Memory Protect Fault.

This bit indicates the

UT1750AR has detected an

access fault, write-protect

fault, or an execute-protect

fault. [0]

14

DMPF

DMA Memory Protect Fault.

This bit indicates a DMA

device has detected an access

fault or a write-protect fault.

[0]

13

MPF

Memory Parity Fault. [0]

12

PCPF

Parallel I/O (PIO) Channel

Parity Fault. [0] No user

access.

11

DCPF

DMA Channel Parity Fault.

[0] No user access.

10

ICF

Illegal Command Fault. This

bit indicates an attempt to

execute an unimplemented or

reserved I/O command. [0]

9

PTF

PIO Transmission Fault. Can

wire-OR I/O error-checking

devices together andfeedthem

into this input to indicate an

error. [0] No user access.

8

SYSFLT

System Fault. [0]

7

IAF

Illegal Address Fault. This bit

indicates addressing a memory

location not physically

present. [0]

6

IIF

5

PIF

Illegal Instruction Fault. This

bit indicates an attempt to

execute a reserved code. [0]

Privileged Instruction Fault.

4

ASF

This bit indicates an attempt to

execute a privileged

instruction with the Processor

State not equal to zero. [0]

Address State Fault. This bit

indicates an attempt to

establish an Address State

value for an unimplemented

page register set. [0]

17