CS4812 Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Fabricante

CS4812 Datasheet PDF : 36 Pages

| |||

CS4812

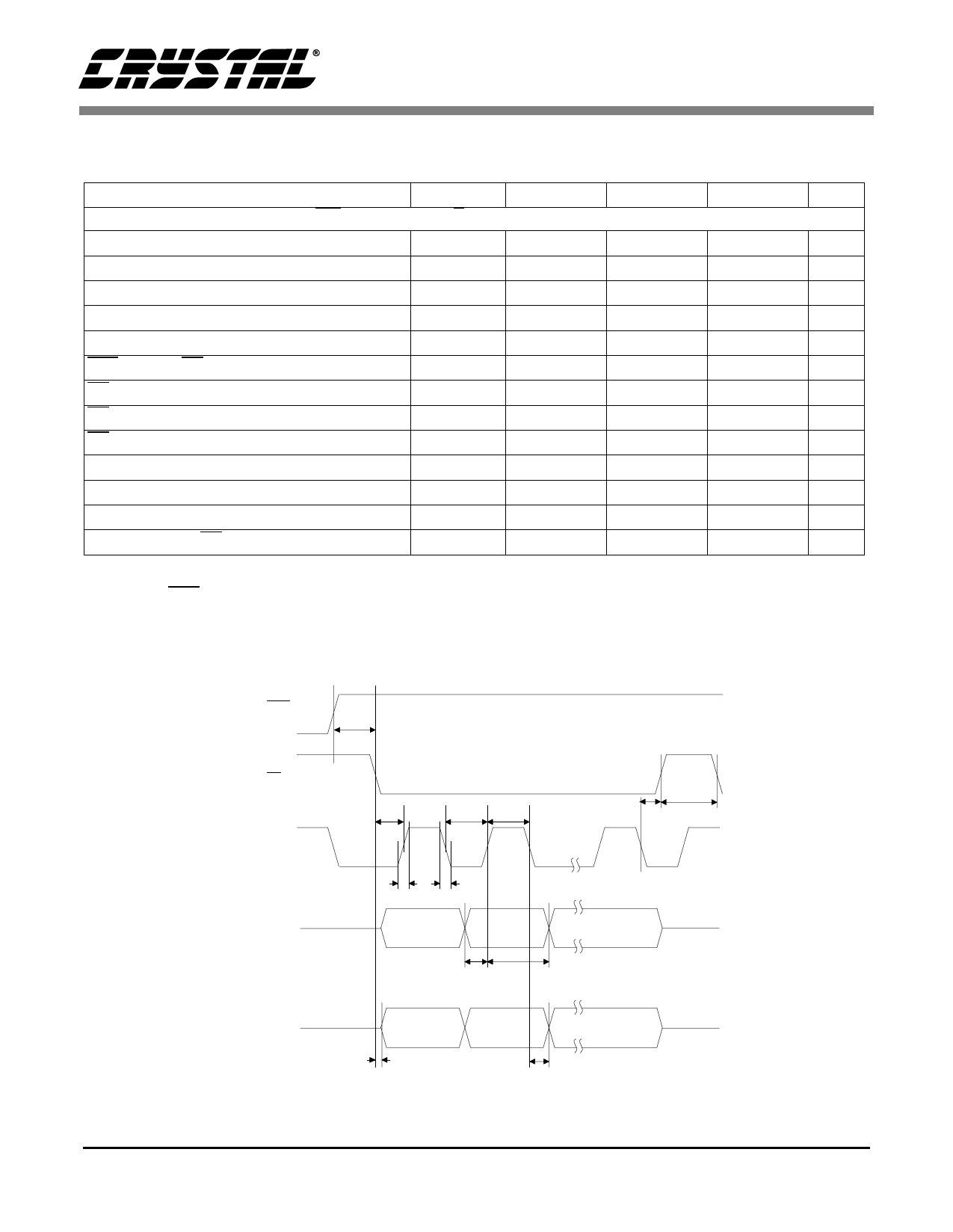

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MASTER

(TA = 25°C, VA, VD = 5V; Inputs: logic 0 = DGND, logic 1 = VD, CL = 30 pF)

Parameter

Symbol

Min

Typ

Max

SPI Master (AutoBoot) Mode (SPI/I2C = 0, SCPM/S = 1, Note 14)

CCLK Clock Frequency

(Note 15)

fsck

CCLK Low Time

tscl

CCLK High Time

tsch

CCLK Rise Time

(Note 16)

tr2

CCLK Fall Time

(Note 16)

tf2

RST rising to CS falling

tsrs

CS High Time Between Transmissions

tcsh

CS Falling to CCLK Edge

tcss

CS Falling to CDOUT valid

tdv

CCLK Falling to CDOUT valid

tpd

CDIN to CCLK Rising Setup Time

tdsu

CCLK Rising to DATA Hold Time

tdh

CCLK Falling to CS rising

tclcs

-

Fs

-

-

1/(2*Fs)

-

-

1/(2*Fs)

-

-

12

-

-

12

-

-

42

-

37

-

-

5

-

-

-

-

50

-

-

100

80

-

-

80

-

-

40

-

-

Units

kHz

ns

ns

ns

ns

µs

µs

µs

ns

ns

ns

ns

ns

Notes: 15. Depending on the input clock configuration, CCLK may be up to 2*Fs temporarily during AutoBoot after

RST is de-asserted and before the control port registers have been initialized.

16. Measured with a 2.2 kΩ pull-up resistor to VD.

RST

t srs

CS

CCLK

CDIN

t css

t scl t sch

t r2

t f2

t clcs

t csh

CDOUT

t dsu t dh

t dv

t pd

Figure 2. SPI Control Port Master Mode (AutoBoot) Timing

DS291PP3

9