LH28F016SC-L Ver la hoja de datos (PDF) - Sharp Electronics

Número de pieza

componentes Descripción

Fabricante

LH28F016SC-L Datasheet PDF : 44 Pages

| |||

LH28F016SC-L/SCH-L

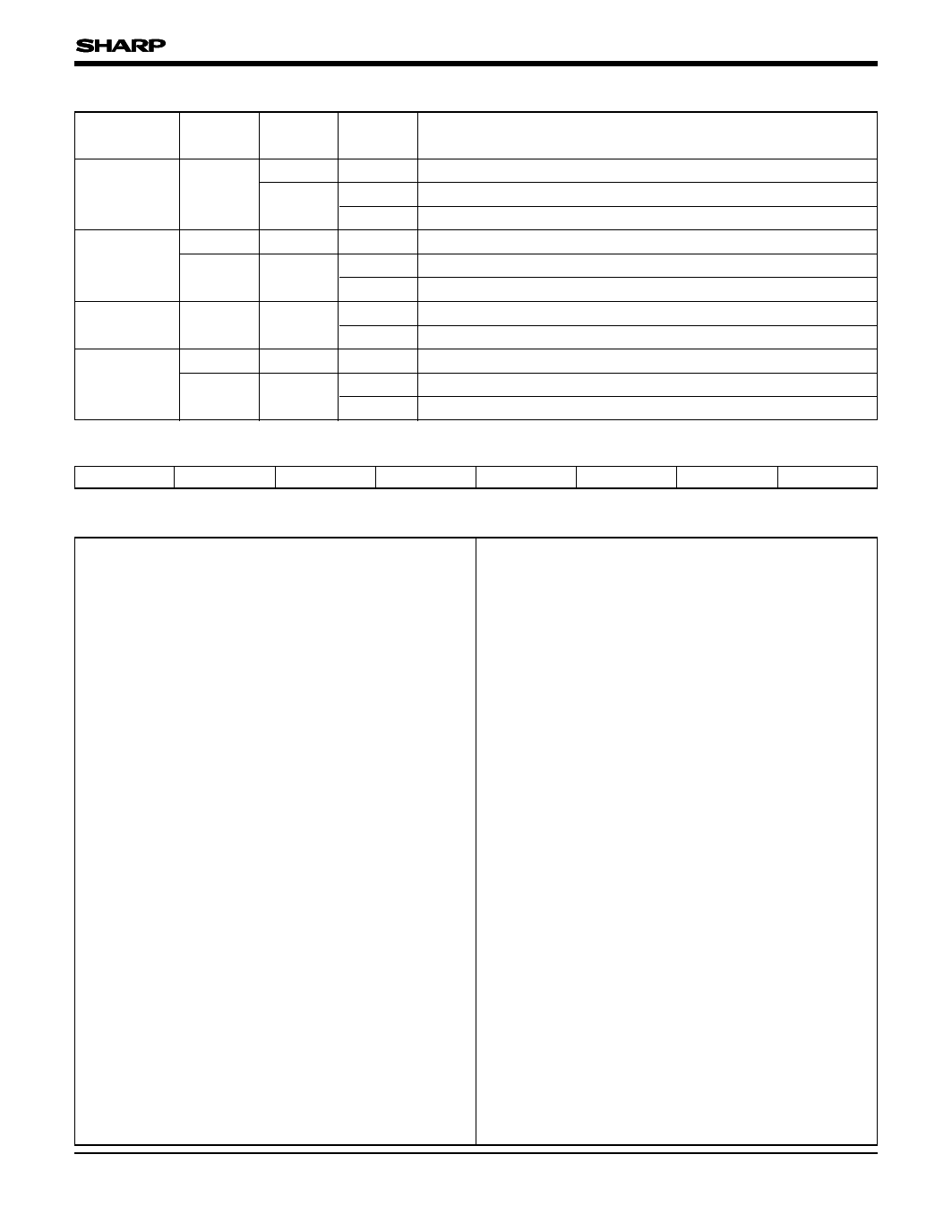

Table 5 Write Protection Alternatives

MASTER BLOCK

OPERATION

RP#

LOCK-BIT LOCK-BIT

EFFECT

Block Erase

or Byte Write

X

0 VIH or VHH Block Erase and Byte Write Enabled

VIH Block is Locked. Block Erase and Byte Write Disabled

1

VHH Block Lock-Bit Override. Block Erase and Byte Write Enabled

Set Block

0

X VIH or VHH Set Block Lock-Bit Enabled

Lock-Bit

1

X

VIH Master Lock-Bit is Set. Set Block Lock-Bit Disabled

VHH Master Lock-Bit Override. Set Block Lock-Bit Enabled

Set Master

X

Lock-Bit

X

VIH Set Master Lock-Bit Disabled

VHH Set Master Lock-Bit Enabled

Clear Block

0

Lock-Bits

1

X VIH or VHH Clear Block Lock-Bits Enabled

X

VIH Master Lock-Bit is Set. Clear Block Lock-Bits Disabled

VHH Master Lock-Bit Override. Clear Block Lock-Bits Enabled

Table 6 Status Register Definition

WSMS

ESS

ECLBS BWSLBS VPPS

BWSS

DPS

R

7

6

5

4

3

2

1

0

SR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

NOTES :

Check RY/BY# or SR.7 to determine block erase, byte write,

or lock-bit configuration completion.

SR.6-0 are invalid while SR.7 = "0".

SR.6 = ERASE SUSPEND STATUS (ESS)

1 = Block Erase Suspended

0 = Block Erase in Progress/Completed

If both SR.5 and SR.4 are "1"s after a block erase or lock-bit

configuration attempt, an improper command sequence was

entered.

SR.5 = ERASE AND CLEAR LOCK-BITS STATUS (ECLBS)

1 = Error in Block Erase or Clear Lock-Bits

0 = Successful Block Erase or Clear Lock-Bits

SR.3 does not provide a continuous indication of VPP level.

The WSM interrogates and indicates the VPP level only after

Block Erase, Byte Write, Set Block/Master Lock-Bit, or Clear

SR.4 = BYTE WRITE AND SET LOCK-BIT STATUS (BWSLBS)

1 = Error in Byte Write or Set Master/Block Lock-Bit

0 = Successful Byte Write or Set Master/Block Lock-Bit

SR.3 = VPP STATUS (VPPS)

1 = VPP Low Detect, Operation Abort

0 = VPP OK

Block Lock-Bits command sequences.

SR.3 is not guaranteed to reports accurate feedback only

when VPP ≠ VPPH1/2/3.

SR.1 does not provide a continuous indication of master and

block lock-bit values. The WSM interrogates the master lock-

bit, block lock-bit, and RP# only after Block Erase, Byte Write,

or Lock-Bit configuration command sequences. It informs the

SR.2 = BYTE WRITE SUSPEND STATUS (BWSS)

1 = Byte Write Suspended

0 = Byte Write in Progress/Completed

SR.1 = DEVICE PROTECT STATUS (DPS)

1 = Master Lock-Bit, Block Lock-Bit and/or RP#

Lock Detected, Operation Abort

0 = Unlock

system, depending on the attempted operation, if the block

lock-bit is set, master lock-bit is set, and/or RP# is not VHH.

Reading the block lock and master lock configuration codes

after writing the Read Identifier Codes command indicates

master and block lock-bit status.

SR.0 is reserved for future use and should be masked out

when polling the status register.

SR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

- 16 -