HFBR-2115T Ver la hoja de datos (PDF) - HP => Agilent Technologies

Número de pieza

componentes Descripción

Fabricante

HFBR-2115T Datasheet PDF : 12 Pages

| |||

Care should be taken to avoid

shorting the receiver Data or

Signal Detect Outputs directly to

ground without proper current-

limiting impedance.

Solder and Wash Process

Compatibility

The transmitter and receiver are

delivered with protective process

caps covering the individual ST*

ports. These process caps protect

the optical subassemblies during

wave solder and aqueous wash

processing and act as dust covers

during shipping.

These data link modules are

compatible with either industry

standard wave- or hand-solder

processes.

Shipping Container

The data link modules are

packaged in a shipping container

designed to protect it from

mechanical and ESD damage

during shipment or storage.

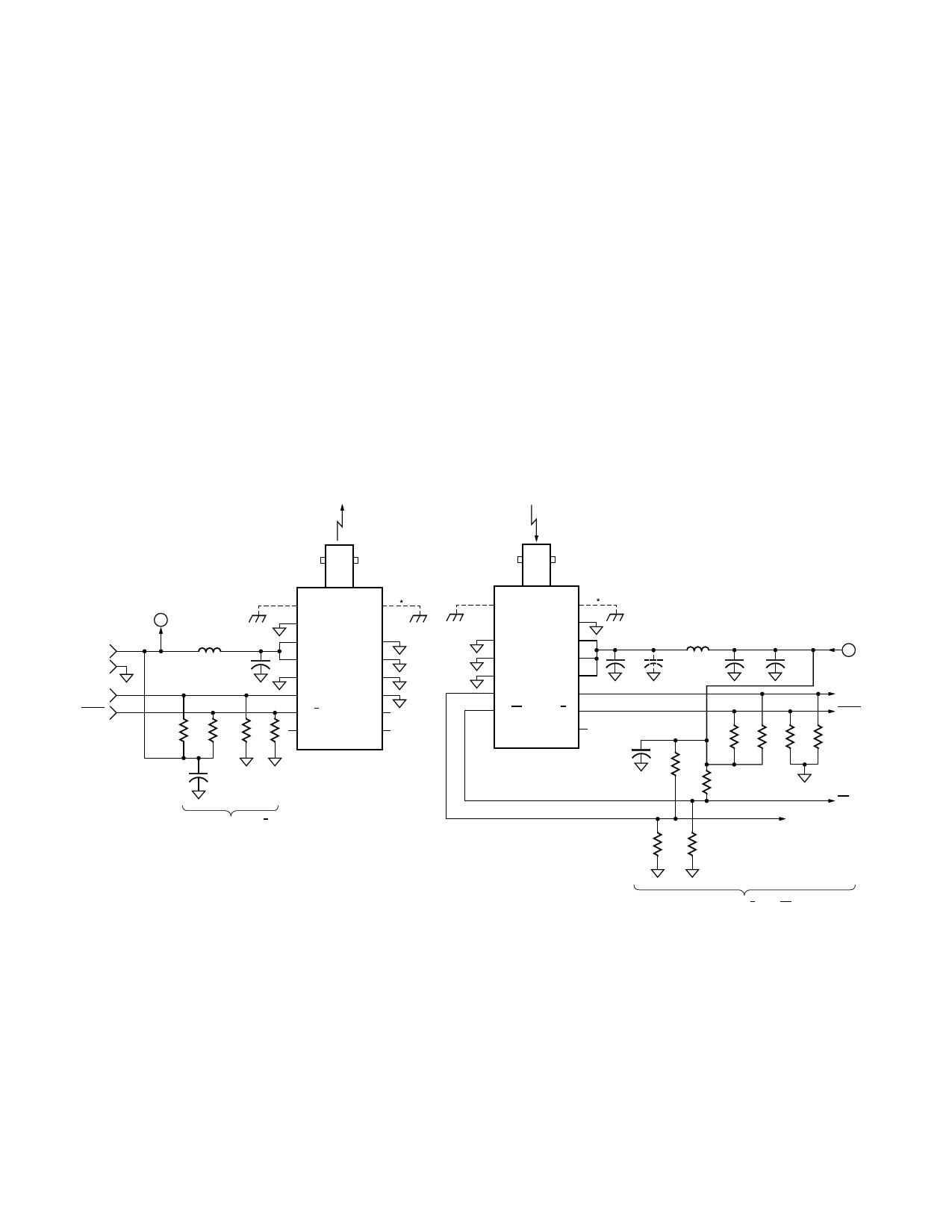

Board Layout–Interface

Circuit and Layout

Guidelines

It is important to take care in the

layout of your circuit board to

achieve optimum performance

from these data link modules.

Figure 7 provides a good example

of a power supply filter circuit that

works well with these parts. Also,

suggested signal terminations for

the Data, Data-bar, Signal Detect

and Signal Detect-bar lines are

shown. Use of a multilayer,

ground-plane printed circuit board

will provide good high-frequency

+5 Vdc

GND

DATA

DATA

Tx

*

A

L2

1

C2

0.1

R3 R2 R4 R1

82 82 130 130

9 NC

10 GND

11 VCC

12 VCC

13 GND

14 D

15 D

16 NC

NC 8

NO

PIN

7

GND 6

GND 5

GND 4

GND 3

VBB 2

NC 1

C5

0.1

TERMINATE D, D

AT Tx INPUTS

Rx

* 9 NC

NC 8

10

NO

PIN

GND 7

11 GND VCC 6

12 GND VCC 5

13 GND VCC 4

14 SD

D3

15 SD

16

NO

PIN

D2

NC 1

TOP VIEWS

L1

1

C1

C7

C3

C4

0.1

10

0.1

10

(OPTIONAL)

R7 R5 R8 R6

82 82 130 130

C6

0.1

R9

82

R11

82

SD

R10 R12

130 130

A

DATA

DATA

SD

TERMINATE D, D, SD, SD AT

INPUTS OF FOLLOW-ON DEVICES

NOTES:

1. RESISTANCE IS IN OHMS. CAPACITANCE IS IN MICROFARADS. INDUCTANCE IS IN MICROHENRIES.

2. TERMINATE TRANSMITTER INPUT DATA AND DATA-BAR AT THE TRANSMITTER INPUT PINS. TERMINATE THE RECEIVER OUTPUT DATA, DATA-BAR, AND SIGNAL DETECT-

BAR AT THE FOLLOW-ON DEVICE INPUT PINS. FOR LOWER POWER DISSIPATION IN THE SIGNAL DETECT TERMINATION CIRCUITRY WITH SMALL COMPROMISE TO THE

SIGNAL QUALITY, EACH SIGNAL DETECT OUTPUT CAN BE LOADED WITH 510 OHMS TO GROUND INSTEAD OF THE TWO RESISTOR, SPLIT-LOAD PECL TERMINATION

SHOWN IN THIS SCHEMATIC.

3. MAKE DIFFERENTIAL SIGNAL PATHS SHORT AND OF SAME LENGTH WITH EQUAL TERMINATION IMPEDANCE.

4. SIGNAL TRACES SHOULD BE 50 OHMS MICROSTRIP OR STRIPLINE TRANSMISSION LINES. USE MULTILAYER, GROUND-PLANE PRINTED CIRCUIT BOARD FOR BEST HIGH-

FREQUENCY PERFORMANCE.

5. USE HIGH-FREQUENCY, MONOLITHIC CERAMIC BYPASS CAPACITORS AND LOW SERIES DC RESISTANCE INDUCTORS. RECOMMEND USE OF SURFACE-MOUNT COIL

INDUCTORS AND CAPACITORS. IN LOW NOISE POWER SUPPLY SYSTEMS, FERRITE BEAD INDUCTORS CAN BE SUBSTITUTED FOR COIL INDUCTORS. LOCATE POWER

SUPPLY FILTER COMPONENTS CLOSE TO THEIR RESPECTIVE POWER SUPPLY PINS. C7 IS AN OPTIONAL BYPASS CAPACITOR FOR IMPROVED, LOW-FREQUENCY NOISE

POWER SUPPLY FILTER PERFORMANCE.

6. DEVICE GROUND PINS SHOULD BE DIRECTLY AND INDIVIDUALLY CONNECTED TO GROUND.

7. CAUTION: DO NOT DIRECTLY CONNECT THE FIBER-OPTIC MODULE PECL OUTPUTS (DATA, DATA-BAR, SIGNAL DETECT, SIGNAL DETECT-BAR, VBB) TO GROUND WITHOUT

PROPER CURRENT LIMITING IMPEDANCE.

8. (*) OPTIONAL METAL ST OPTICAL PORT TRANSMITTER AND RECEIVER MODULES WILL HAVE PINS 8 AND 9 ELECTRICALLY CONNECTED TO THE METAL PORT ONLY AND

NOT CONNECTED TO THE INTERNAL SIGNAL GROUND.

Figure 7. Recommended Interface Circuitry and Power Supply Filter Circuits.

181