HSP45314 Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Fabricante

HSP45314 Datasheet PDF : 14 Pages

| |||

HSP45314

Functional Description

The HSP45314 is an NCO with an integrated 14-bit DAC

designed to run in excess of 125MSPS. The NCO is a 16-bit

output design, which is rounded to 14 bits for input to the

DAC. The frequency control is the sum of a 48-bit center

frequency word and a 48-bit offset frequency word. The two

components are added modulo 48 bits with the alignment

shown in Table 1. Each of the two terms can be zeroed

independently (via the microprocessor interface for the

center frequency and via the ENOFR pin for the offset

frequency term).

Frequency Generation

The output frequency of the part is determined by the

summation of two registers:

fOUT = fCLK x ( (CF + OF) mod (248))/ (248),

where CF is the Center Frequency register and OF is the

Offset Frequency register.

With a 125MSPS clock rate, the center frequency can be

programmed to

(125 x 106)/(248) = 0.4 µHz resolution.

The addition of the frequency control words can be

interpreted as two’s complement if convenient. For example,

if the center frequency is set to 4000...00h and the offset

frequency set to C000..00h, the programmed center

frequency would be fCLK/4 and the programmed offset

frequency -fCLK/4. The sum would be 10000..00h, but

because only the lower 48 bits are retained, the effective

frequency would be 0. In reality, frequencies above

8000...00h alias below fCLK/2 (the output of the part is real),

so the MSB is only provided as a convenience for two’s

complement calculations.

The frequency control of the NCO is the change in phase per

clock period or dφ/dt. This is integrated by the phase

accumulator to obtain frequency. The most significant 24

bits of phase are then mapped to 16 bits of amplitude in a

sine look-up table function. The range of dφ/dt is 0 to 1 with

1 equaling 360 degrees or (2 x pi) per clock period. The

phase accumulator output is also 0 to 1 with 1 equaling 360

degrees. The operations are modulo 48 bits because the

MSB (bit 47) aligns with the most significant address bit of

the sine ROM and the ROM contains one cycle of a

sinusoid. The MSB is weighted at 180 degrees. Full scale is

360 degrees minus 1 LSB and the phase then rolls over to 0

degrees for the next cycle of the sinusoid.

Parallel Interface

The processor interface is an 8-bit parallel write only

interface. The interface consists of 8 data bits (C7:C0), four

address pins (A3:A0), a Write Strobe (WR), and a Write

Enable (WE). The interface is a master/slave type. The

processor interface loads a set of master registers. The

contents of the master set of registers is then transferred to

a slave set of registers by asserting a pin (UPDATE). This

allows all of the bits of the frequency control to be updated

simultaneously.

The rate which the user writes (WR) to these registers does

not have to be the same rate as the DDS clock rate (the rate

of the NCO and DAC; pin CLK). It is expected that most

applications will have a slower register write rate than the

DDS clock rate. It takes 6 WR cycles at the write rate plus

another 11 CLK cycles at the DDS rate to write and obtain a

new frequency, assuming that all registers are rewritten and

the UPDATE pin is always active. If the UPDATE pin is not

active until after the new word has been written, it takes 14

CLK cycles, rather than 11. For cases which require the

output to be updated with all of the new frequency

information present, it is necessary that the UPDATE be

inactive until after all of the new frequency word has been

written to the device. See the Timing Diagrams for more

information. The parallel registers can be written to again

immediately after the 11th or 14th CLK cycle, again

depending the state of UPDATE. If the application does not

need 48 bits (all 6 registers) of frequency information, then

the output frequency can be changed more quickly. For

example, if only 32 bits of frequency information are needed

and it is desired that the output be updated all at once, then

it takes 4 WR cycles, then the assertion low of the UPDATE

pin, plus another 14 CLK cycles at the DDS rate to write and

update a new frequency.

The timing is the same whether writing to the center or offset

frequency registers. For faster frequency update, consider

the ENOFR (Enable Offset Frequency Register) option.

Once the values have been written to the center and offset

frequency registers, the user can enable and disable the

offset frequency register, which is added to the center

frequency value when enabled. The ENOFR pin has a

latency of 14 CLK cycles, but simplifies the interface

because the only pin that has to be toggled is the ENOFR

pin.

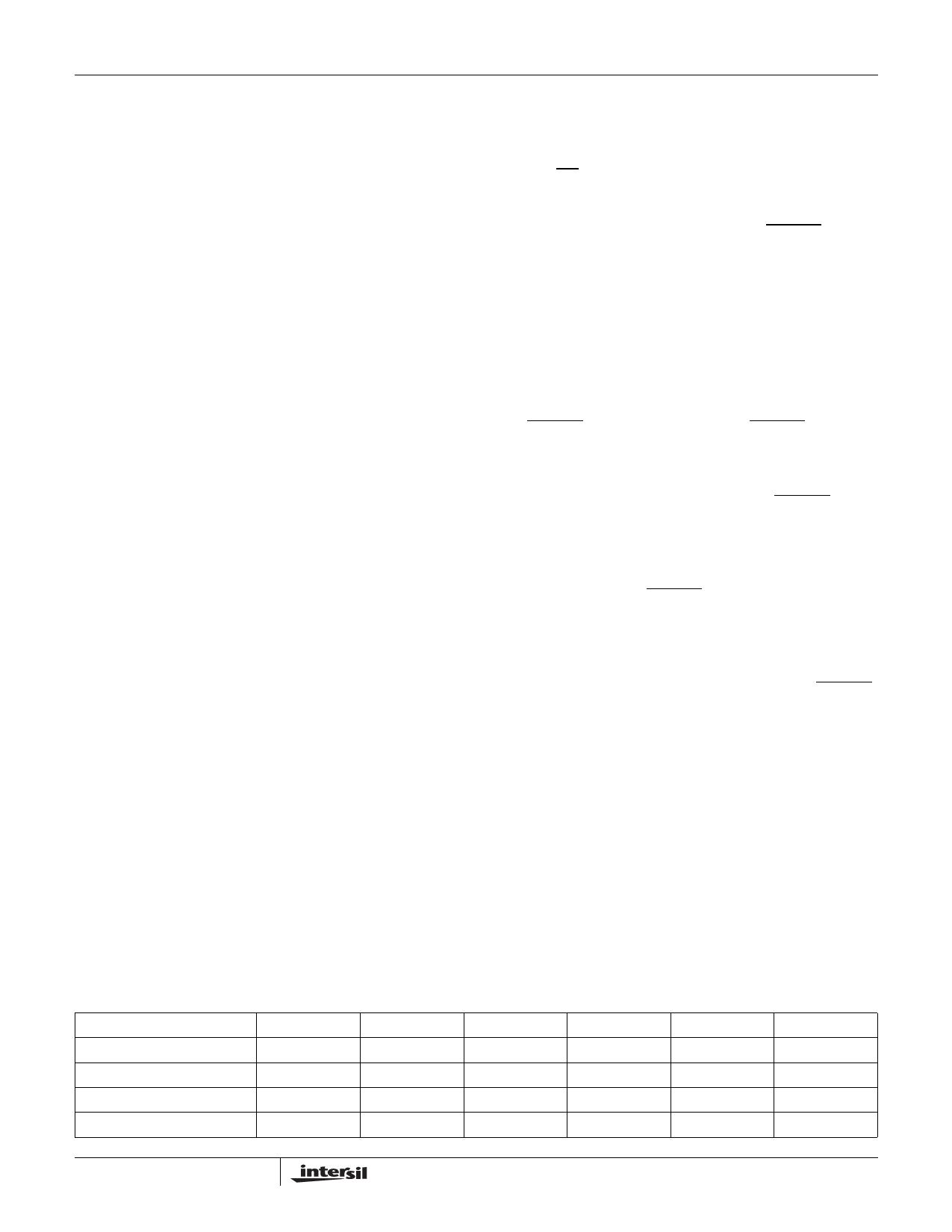

Bits

Individual Bit Alignment

Phase Accumulator

Center Frequency

Offset Frequency

TABLE 1. FREQUENCY CONTROL BIT ALIGNMENTS

4444 4444

3333 3333

3322 2222

2222 1111

7654 3210

9876 5432

1098 7654

3210 9876

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

xxxx xxxx

1111 1100

5432 1098

xxxx xxxx

xxxx xxxx

xxxx xxxx

0000 0000

7654 3210

xxxx xxxx

xxxx xxxx

xxxx xxxx

3