M80C186 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

M80C186 Datasheet PDF : 59 Pages

| |||

M80C186

Single-Step Interrupt

The M80C186 has an internal interrupt that allows

programs to execute one instruction at a time It is

called the single-step interrupt and is controlled by

the single-step flag bit (TF) in the Status Word Once

this bit is set an internal single-step interrupt will

occur after the next instruction has been executed

The interrupt clears the TF bit and uses an internally

supplied vector of 1 The IRET instruction is used to

set the TF bit and transfer control to the next instruc-

tion to be single-stepped

Initialization and Processor Reset

Processor initialization or startup is accomplished by

driving the RES input pin LOW RES forces the

M80C186 to terminate all execution and local bus

activity No instruction or bus activity will occur as

long as RES is active After RES becomes inactive

and an internal processing interval elapses the

M80C186 begins execution with the instruction at

physical location FFFF0(H) RES also sets some

registers to predefined values as shown in Table 5

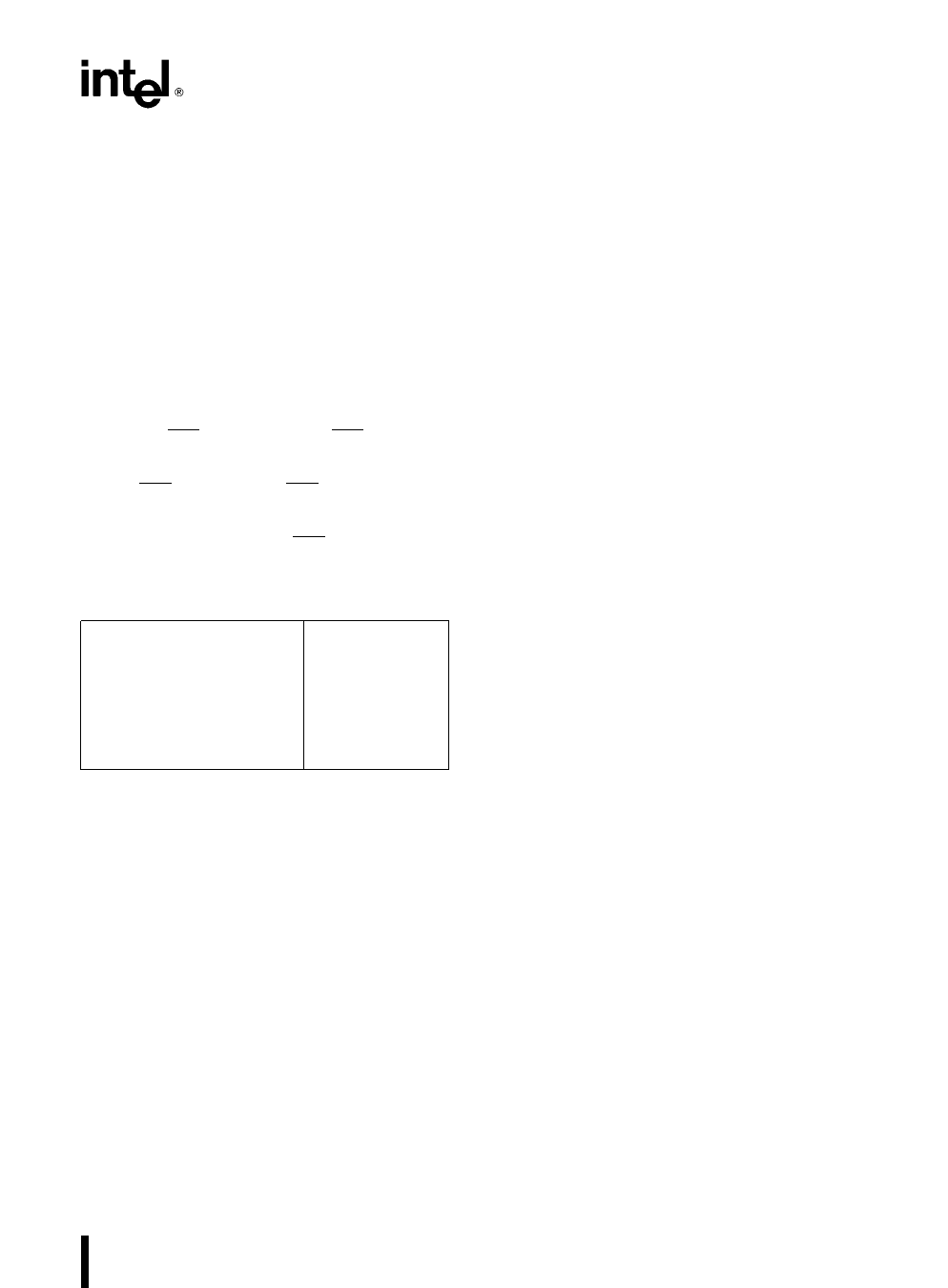

Table 5 M80C186 Initial Register State

after RESET

Status Word

Instruction Pointer

Code Segment

Data Segment

Extra Segment

Stack Segment

Relocation Register

UMCS

F002(H)

0000(H)

FFFF(H)

0000(H)

0000(H)

0000(H)

20FF(H)

FFFB(H)

M80C186 CLOCK GENERATOR

The M80C186 provides an on-chip clock generator

for both internal and external clock generation The

clock generator features a crystal oscillator a divide-

by-two counter synchronous and asynchronous

ready inputs and reset circuitry

Oscillator

The M80C186 oscillator circuit is designed to be

used with either a parallel resonant fundamental or

third-overtone mode crystal depending upon the

frequency range of the application as shown in Fig-

ure 8a This is used as the time base for the

M80C186 The crystal frequency chosen should be

twice the required processor frequency Use of an

LC or RC circuit is not recommended

The oscillator output is not directly available external

to the M80C186 The two recommended crys-

tal configurations are shown in Figures 8b and 8c

When used in third-overtone mode the tank circuit

shown in Figure 8b is recommended for stable oper-

ation The sum of the stray capacitances and load-

ing capacitors should equal the values shown It is

advisable to limit stray capacitance between the X1

and X2 pins to less than 10 pF While a fundamen-

tal-mode circuit will require approximately 1 ms for

start-up the third-overtone arrangement may require

1 ms to 3 ms to stabilize

Alternately the oscillator pins may be driven from an

external source as shown in Figure 8d or Figure 8e

The configuration shown in Figure 8f is not recom-

mended

The following parameters may be used for choosing

a crystal

Temperature Range

b55 C to a125 C

ESR (Equivalent Series Resistance)

40X max

C0 (Shunt Capacitance of Crystal)

C1 (Load Capacitance)

Drive Level

7 0 pf max

20 pF g 2 pF

1 mW max

Clock Generator

The M80C186 clock generator provides the 50%

duty cycle processor clock for the M80C186 It does

this by dividing the oscillator output by 2 forming the

symmetrical clock If an external oscillator is used

the state of the clock generator will change on the

falling edge of the oscillator signal The CLKOUT pin

provides the processor clock signal for use outside

the M80C186 This may be used to drive other sys-

tem components All timings are referenced to the

output clock

READY Synchronization

The M80C186 provides both synchronous and asyn-

chronous ready inputs Asynchronous ready syn-

chronization is accomplished by circuitry which sam-

ples ARDY in the middle of T2 T3 and again in the

middle of each TW until ARDY is sampled HIGH

One-half CLKOUT cycle of resolution time is used

Full synchronization is performed only on the rising

edge of ARDY i e the falling edge of ARDY must

be synchronized to the CLKOUT signal if it will occur

during T2 T3 or TW High-to-LOW transitions of

ARDY must be performed synchronously to the CPU

clock

A second ready input (SRDY) is provided to inter-

face with externally synchronized ready signals This

input is sampled at the end of T2 T3 and again at

the end of each TW until it is sampled HIGH By

using this input rather than the asynchronous ready

input the half-clock cycle resolution time penalty is

eliminated

17