M80C186 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

M80C186 Datasheet PDF : 59 Pages

| |||

M80C186

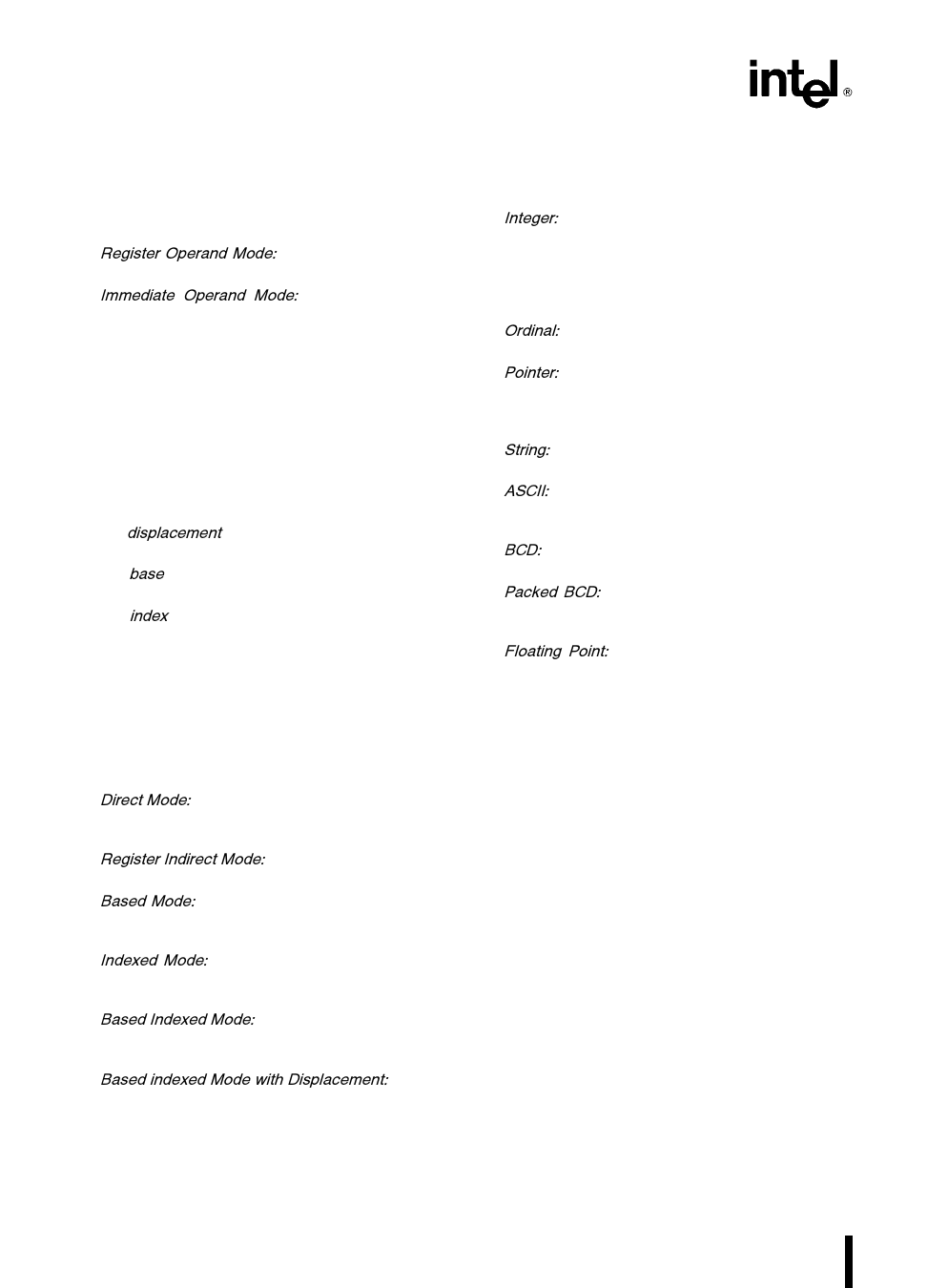

Addressing Modes

The M80C186 provides eight categories of address-

ing modes to specify operands Two addressing

modes are provided for instructions that operate on

register or immediate operands

Register Operand Mode The operand is located

in one of the 8- or 16-bit general registers

Immediate Operand Mode The operand is in-

cluded in the instruction

Six modes are provided to specify the location of an

operand in a memory segment A memory operand

address consists of two 16-bit components a seg-

ment base and an offset The segment base is sup-

plied by a 16-bit segment register either implicitly

chosen by the addressing mode or explicitly chosen

by a segment override prefix The offset also called

the effective address is calculated by summing any

combination of the following three address ele-

ments

the displacement (an 8- or 16-bit immediate value

contained in the instruction)

the base (contents of either the BX or BP base

registers) and

the index (contents of either the SI or DI index

registers)

Any carry out from the 16-bit addition is ignored

Eight-bit displacements are sign extended to 16-bit

values

Combinations of these three address elements de-

fine the six memory addressing modes described

below

Direct Mode The operand’s offset is contained in

the instruction as an 8- or 16-bit displacement el-

ement

Register Indirect Mode The operand’s offset is in

one of the registers SI DI BX or BP

Based Mode The operand’s offset is the sum of

an 8- or 16-bit displacement and the contents of

a base register (BX or BP)

Indexed Mode The operand’s offset is the sum

of an 8- or 16-bit displacement and the contents

of an index register (SI or DI)

Based Indexed Mode The operand’s offset is the

sum of the contents of a base register and an

Index register

Based indexed Mode with Displacement The op-

erand’s offset is the sum of a base register’s con-

tents an index register’s contents and an 8- or

16-bit displacement

14

Data Types

The M80C186 directly supports the following data

types

Integer A signed binary numeric value contained

in an 8-bit byte or a 16-bit word All operations

assume a 2’s complement representation

Signed 32- and 64-bit integers are supported us-

ing a Numeric Data Coprocessor with the

M80C186

Ordinal An unsigned binary numeric value con-

tained in an 8-bit byte or a 16-bit word

Pointer A 16- or 32-bit quantity composed of a

16-bit offset component or a 16-bit segment base

component in addition to a 16-bit offset compo-

nent

String A contiguous sequence of bytes or words

A string may contain from 1 to 64K bytes

ASCII A byte representation of alphanumeric and

control characters using the ASCII standard of

character representation

BCD A byte (unpacked) representation of the

decimal digits 0 – 9

Packed BCD A byte (packed) representation of

two decimal digits (0 – 9) One digit is stored in

each nibble (4-bits) of the byte

Floating Point A signed 32- 64- or 80-bit real

number representation (Floating point operands

are supported using a Numeric Data Coprocessor

with the M80C186 )

In general individual data elements must fit within

defined segment limits Figure 7 graphically repre-

sents the data types supported by the M80C186

I O Space

The I O space consists of 64K 8-bit or 32K 16-bit

ports Separate instructions address the I O space

with either an 8-bit port address specified in the in-

struction or a 16-bit port address in the DX register

8-bit port addresses are zero extended such that

A15 – A8 are LOW I O port addresses 00F8(H)

through 00FF(H) are reserved

Interrupts

An interrupt transfers execution to a new program

location The old program address (CS IP) and ma-

chine state (Status Word) are saved on the stack to

allow resumption of the interrupted program Inter-

rupts fall into three classes hardware initiated INT

instructions and instruction exceptions Hardware

initiated interrupts occur in response to an external

input and are classified as non-maskable or maska-

ble