M80C186 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

M80C186 Datasheet PDF : 59 Pages

| |||

M80C186

270500 –7

NOTE

Supported by using a Numeric Data Coprocessor with

the M80C186

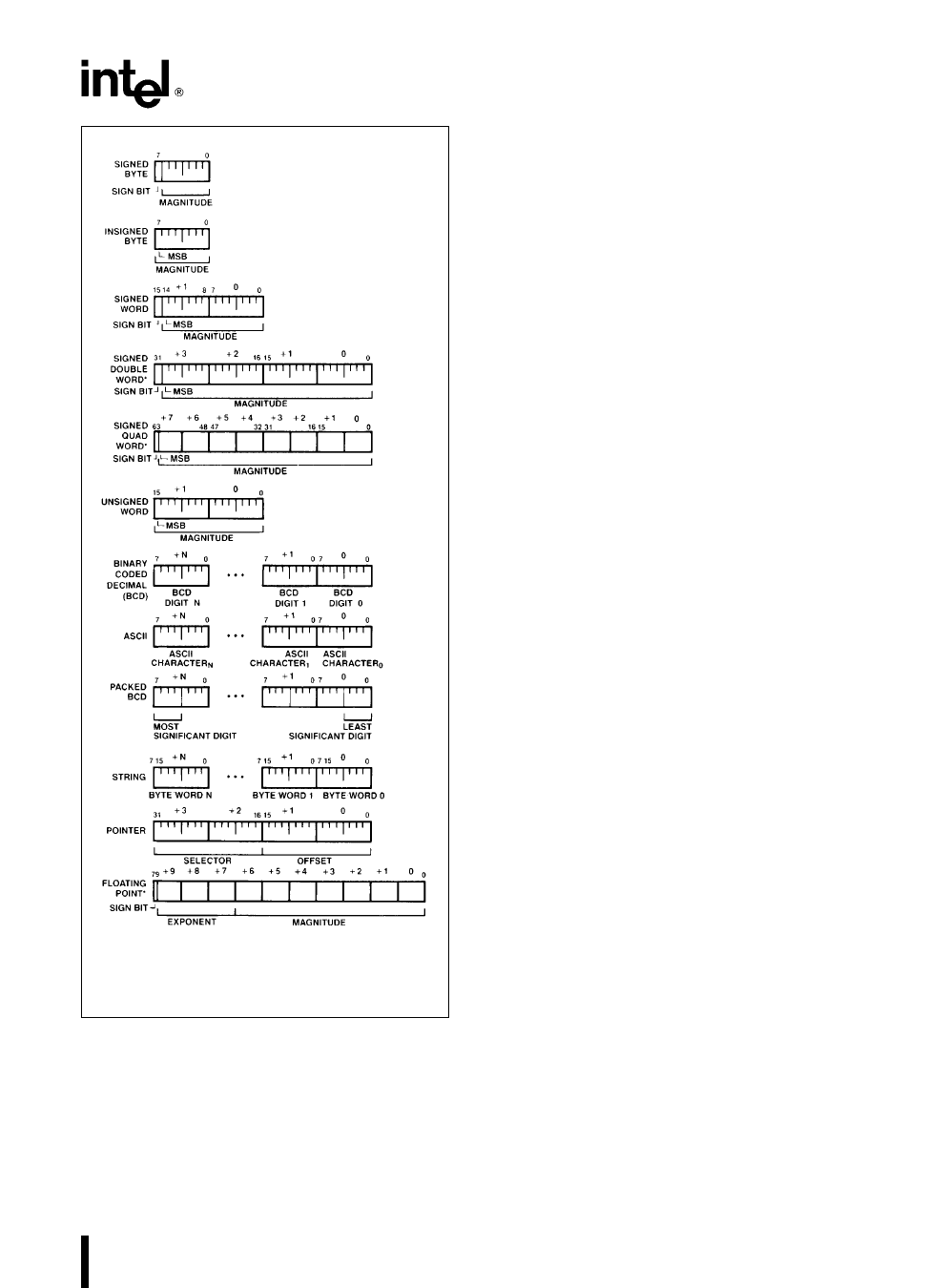

Figure 7 M80C186 Supported Data Types

Programs may cause an interrupt with an INT in-

struction Instruction exceptions occur when an un-

usual condition which prevents further instruction

processing is detected while attempting to execute

an instruction If the exception was caused by exe-

cuting an ESC instruction with the ESC trap bit set in

the relocation register the return instruction will

point to the ESC instruction or to the segment over-

ride prefix immediately preceding the ESC instruc-

tion if the prefix was present In all other cases the

return address from an exception will point at the

instruction immediately following the instruction

causing the exception

A table containing up to 256 pointers defines the

proper interrupt service routine for each interrupt In-

terrupts 0 – 31 some of which are used for instruc-

tion exceptions are reserved Table 4 shows the

M80C186 predefined types and default priority lev-

els For each interrupt an 8-bit vector must be sup-

plied to the M80C186 which identifies the appropri-

ate table entry Exceptions supply the interrupt

vector internally In addition internal peripherals and

noncascaded external interrupts will generate their

own vectors through the internal interrupt controller

INT instructions contain or imply the vector and al-

low access to all 256 interrupts Maskable hardware

initiated interrupts supply the 8-bit vector to the CPU

during an interrupt acknowledge bus sequence

Non-maskable hardware interrupts use a predefined

internally supplied vector

Interrupt Sources

The M80C186 can service interrupts generated by

software or hardware The software interrupts are

generated by specific instructions (INT ESC unused

OP etc ) or the results of conditions specified by

instructions (array bounds check INT0 DIV IDIV

etc ) All interrupt sources are serviced by an indirect

call through an element of a vector table This vector

table is indexed by using the interrupt vector type

(Table 4) multiplied by four All hardware-generated

interrupts are sampled at the end of each instruc-

tion Thus the software interrupts will begin service

first Once the service routine is entered and inter-

rupts are enabled any hardware source of sufficient

priority can interrupt the service routine in progress

The software generated M80C186 interrupts are de-

scribed below

DIVIDE ERROR EXCEPTION (TYPE 0)

Generated when a DIV or IDIV instruction quotient

cannot be expressed in the number of bits in the

destination

SINGLE-STEP INTERRUPT (TYPE 1)

Generated after most instructions if the TF flag is

set Interrupts will not be generated after prefix in-

structions (e g REP) instructions which modify seg-

ment registers (e g POP DS) or the WAIT instruc-

tion

NON-MASKABLE INTERRUPT NMI (TYPE 2)

An external interrupt source which cannot be

masked

15