PCF8558 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Fabricante

PCF8558 Datasheet PDF : 24 Pages

| |||

Philips Semiconductors

Universal LCD driver for small graphic

panels

Objective specification

PCF8558

CHARACTERISTICS OF THE I2C-BUS

The I2C-bus is for bidirectional, two-line communication

between different ICs or modules. The two lines are a

serial data line (SDA) and a serial clock line (SCL) which

must be connected to a positive supply via a pull-up

resistor. Data transfer may be initiated only when the bus

is not busy.

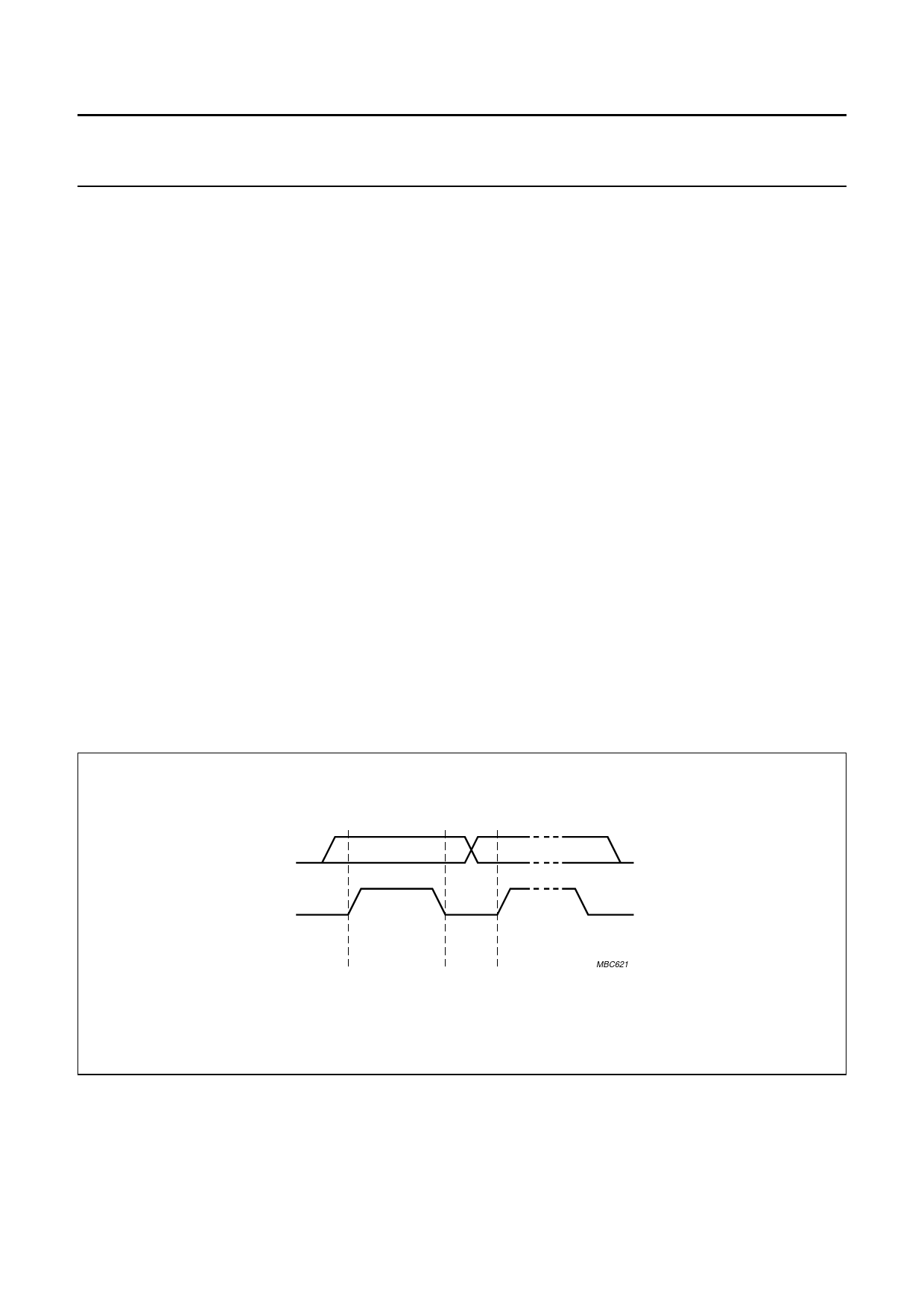

Bit transfer

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable during the

HIGH period of the clock pulse as changes in the data line

at this moment will be interpreted as control signals.

START and STOP conditions

Both data and clock lines remain HIGH when the bus is not

busy. A HIGH-to-LOW transition of the data line, while the

clock is HIGH, is defined as the START condition (S).

A LOW-to-HIGH transition of the data line while the clock

is HIGH, is defined as the STOP condition (P).

Acknowledge

The number of data bytes transferred between the START

and STOP conditions from transmitter to receiver is

unlimited. Each data byte of eight bits is followed by one

acknowledge bit. The acknowledge bit is a HIGH level put

on the bus by the transmitter, whereas the master

generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an

acknowledge after the reception of each byte. Also a

master must generate an acknowledge after the reception

of each byte that has been clocked out of the slave

transmitter. The device that acknowledges must pull down

the SDA line during the acknowledge clock pulse, so that

the SDA line is stable LOW during the HIGH period of the

acknowledge related clock pulse (set-up and hold times

must be taken into consideration). A master receiver must

signal the end of a data transmission to the transmitter by

not generating an acknowledge on the last byte that has

been clocked out of the slave. In this event the transmitter

must leave the data line HIGH to enable the master to

generate a stop condition.

System configuration

A device transmitting a message is a 'transmitter', a device

receiving a message is the 'receiver'. The device that

controls the message flow is the 'master' and the devices

which are controlled by the master are the 'slaves'.

handbook, full pagewidth

SDA

SCL

data line

stable;

data valid

change

of data

allowed

Fig.7 Bit transfer.

MBC621

1998 Apr 07

11