E28F004BL-T150 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

E28F004BL-T150 Datasheet PDF : 44 Pages

| |||

28F400BL-T B 28F004BL-T B

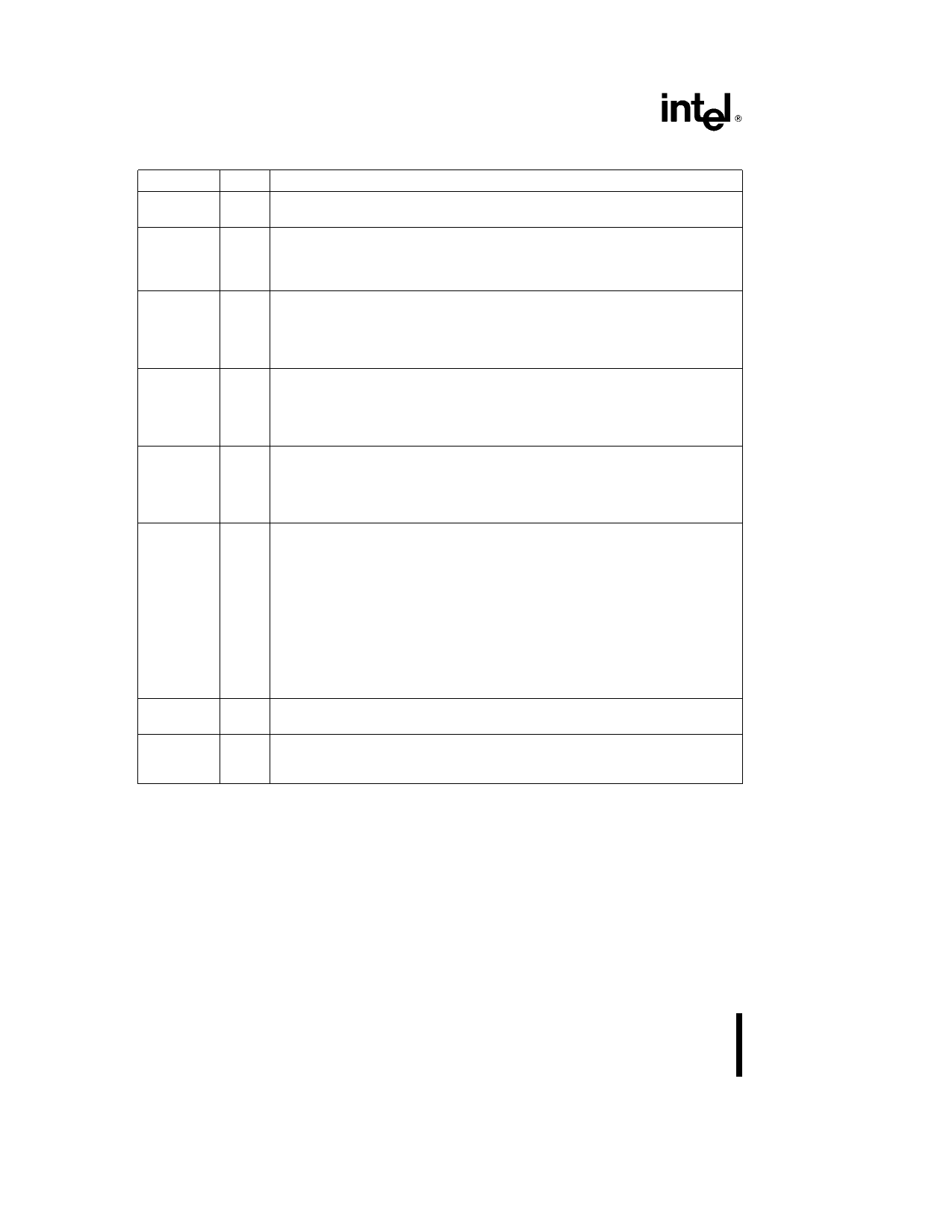

1 5 Pin Descriptions for x8 x16 28F400BL

Symbol Type

Name and Function

A0 – A17

I

ADDRESS INPUTS for memory addresses Addresses are internally latched

during a write cycle

A9

I

ADDRESS INPUT When A9 is at 12V the signature mode is accessed During this

mode A0 decodes between the manufacturer and device ID’s When BYTE is at

a logic low only the lower byte of the signatures are read DQ15 Ab1 is a don’t

care in the signature mode when BYTE is low

DQ0 – DQ7

I O DATA INPUTS OUTPUTS Inputs array data on the second CE and WE cycle

during a program command Inputs commands to the command user interface

when CE and WE are active Data is internally latched during the write and

program cycles Outputs array Intelligent Identifier and status register data The

data pins float to tri-state when the chip is deselected or the outputs are disabled

DQ8 – DQ15 I O DATA INPUT OUTPUTS Inputs array data on the second CE and WE cycle

during a program command Data is internally latched during the write and program

cycles The data pins float to tri-state when the chip is deselected or the outputs

are disabled as in the byte-wide mode (BYTE e‘‘0’’) In the byte-wide mode

DQ15 Ab1 becomes the lowest order address for data output on DQ0 – DQ7

CE

I

CHIP ENABLE Activates the device’s control logic input buffers decoders and

sense amplifiers CE is active low CE high deselects the memory device and

reduces power consumption to standby levels If CE and RP are high but not

at a CMOS high level the standby current will increase due to current flow through

the CE and RP input stages

RP

I

RESET DEEP POWER-DOWN Provides Three-State control Puts the device in

deep power-down mode Locks the boot block from program erase

When RP is at logic high level and equals 4 1V maximum the boot block is

locked and cannot be programmed or erased

When RP e 11 4V minimum the boot block is unlocked and can be programmed

or erased

When RP is at a logic low level the boot block is locked the deep power-down

mode is enabled and the WSM is reset preventing any blocks from being

programmed or erased therefore providing data protection during power

transitions When RP transitions from logic low to logic high the flash memory

enters the read-array mode

OE

I

OUTPUT ENABLE Gates the device’s outputs through the data buffers during a

read cycle OE is active low

WE

I

WRITE ENABLE Controls writes to the Command Register and array blocks

WE is active low Addresses and data are latched on the rising edge of the WE

pulse

8