CDP1802AC/3 Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Fabricante

CDP1802AC/3 Datasheet PDF : 27 Pages

| |||

CDP1802AC/3

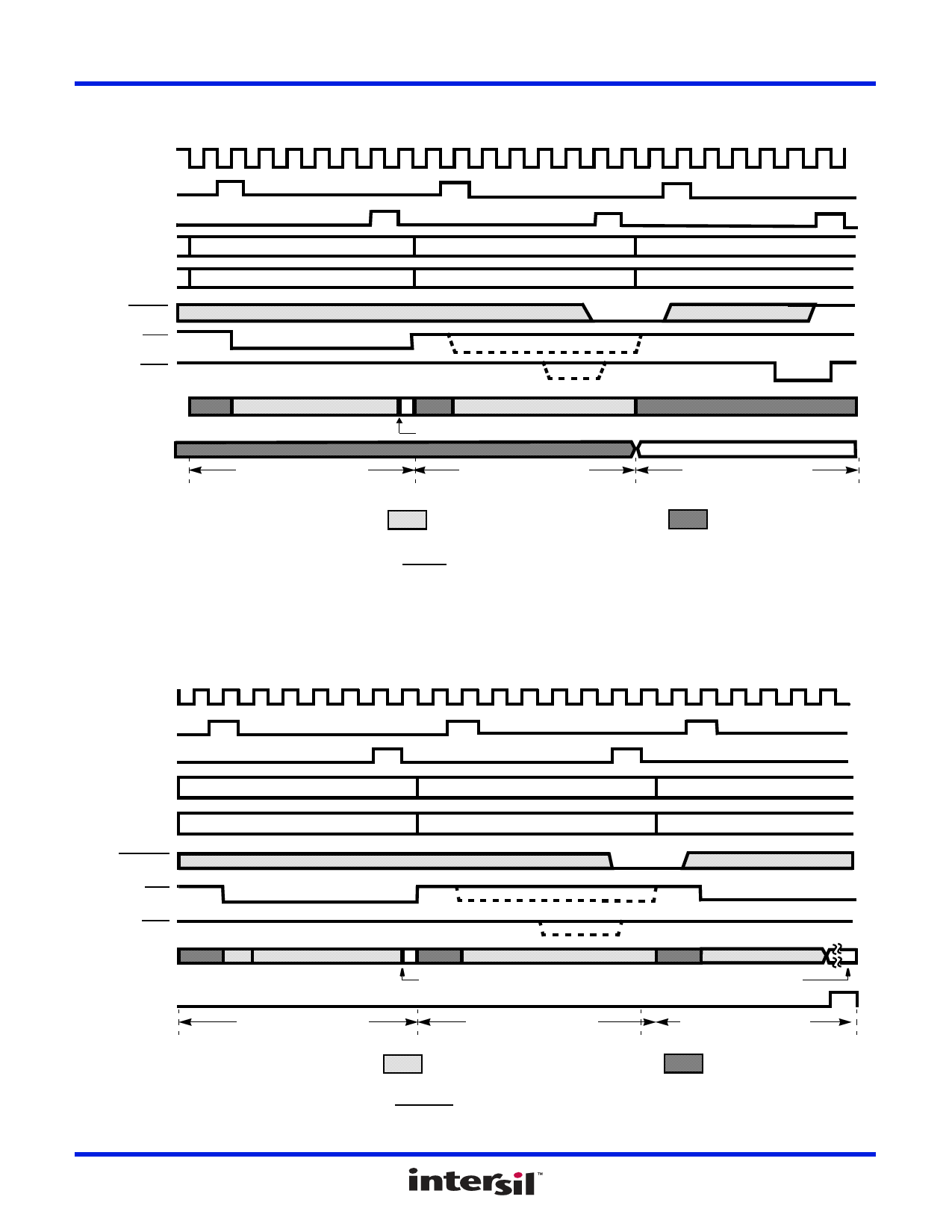

Machine Cycle Timing Waveforms (Propagation Delays Not Shown) (Continued)

0 1 2 3 4 56 7 0 12 3 4 5 6 7 01 2 34 5 6 7

CLOCK

TPA

TPB

MACHINE

CYCLE

INSTRUCTION

CYCLE n

FETCH (S0)

CYCLE (n+1)

EXECUTE (S1)

CYCLE (n+2)

DMA (S2)

DMA-IN

MRD

MWR

MEMORY

OUTPUT

DATA BUS

(NOTE)

MEMORY READ CYCLE

VALID OUTPUT

MEMORY READ, WRITE

OR NON-MEMORY CYCLE

VALID DATA FROM INPUT DEVICE

MEMORY WRITE CYCLE

NOTE: USER GENERATED SIGNAL

“DON’T CARE” OR INTERNAL DELAYS

HIGH IMPEDANCE STATE

FIGURE 10. DMA IN CYCLE TIMING WAVEFORMS

01234567012345670123456

CLOCK

TPA

TPB

MACHINE

CYCLE

CYCLE n

CYCLE (n + 1)

CYCLE (n + 2)

INSTRUCTION

FETCH (S0)

EXECUTE (S1)

DMA (S2)

DMA OUT

(NOTE)

MRD

MWR

MEMORY

OUTPUT

DATA

STROBE

(S2 ² TPB)

(NOTE)

MEMORY READ CYCLE

NOTE: USER GENERATED SIGNAL

VALID OUTPUT

VALID DATA FROM MEMORY

MEMORY READ, WRITE

OR NON-MEMORY CYCLE

“DON’T CARE” OR INTERNAL DELAYS

MEMORY READ CYCLE

HIGH IMPEDANCE STATE

FIGURE 11. DMA OUT CYCLE TIMING WAVEFORMS

FN1441 Rev 3.00

October 17, 2008

Page 12 of 27