AS4LC1M16S0 Ver la hoja de datos (PDF) - Alliance Semiconductor

NĂșmero de pieza

componentes DescripciĂłn

Fabricante

AS4LC1M16S0 Datasheet PDF : 29 Pages

| |||

AS4LC2M8S1

AS4LC1M16S1

Âź

Functional description

The AS4LC2M8S1, AS4LC2M8S0, and AS4LC1M16S1, AS4LC1M16S0 are high-performance 16-megabit CMOS Synchronous Dynamic

Random Access Memory (SDRAM) devices organized as 1,048,576 words Ă 8 bits Ă 2 banks (2048 rows Ă 512 columns) and 524,288

words Ă 16 bits Ă 2 banks (2048 rows Ă 256 columns), respectively. Very high bandwidth is achieved using a pipelined architecture where

all inputs and outputs are referenced to the rising edge of a common clock. Programmable burst mode can be used to read up to a full page

of data (512 bytes for 2M Ă 8 and 256 bytes for 1M Ă 16) without selecting a new column address.

The operational advantages of an SDRAM are as follows: (1) the ability to synchronously output data at a high clock frequency with

automatic increments of column-address (burst access); (2) bank-interleaving, which hides precharge time and attains seamless operation;

and (3) the capability to change column-address randomly on every clock cycle during burst access.

This SDRAM product also features a programmable mode register, allowing users to select read latency as well as burst length and type

(sequential or interleaved). Lower latency improves first data access in terms of CLK cycles, while higher latency improves maximum

frequency of operation. This feature enables flexible performance optimization for a variety of applications.

SDRAM commands and functions are decoded from control inputs. Basic commands are as follows:

âą Mode register set

âą Deactivate bank

âą Deactivate all banks

âą Select column; write

âą Select column; read

âą Deselect; power down

âą Auto precharge with read/write âą Self-refresh

âą Select row; activate bank

âą CBR refresh

Both devices are available in 400-mil plastic TSOP type 2 package. The AS4LC2M8S1/ AS4LC2M8S0 have 44 pins, and the AS4LC1M16S1/

AS4LC1M16S0 have 50 pins. All devices operate with a power supply of 3.3V ± 0.3V. Multiple power and ground pins are provided for low

switching noise and EMI. Inputs and outputs are LVTTL compatible.

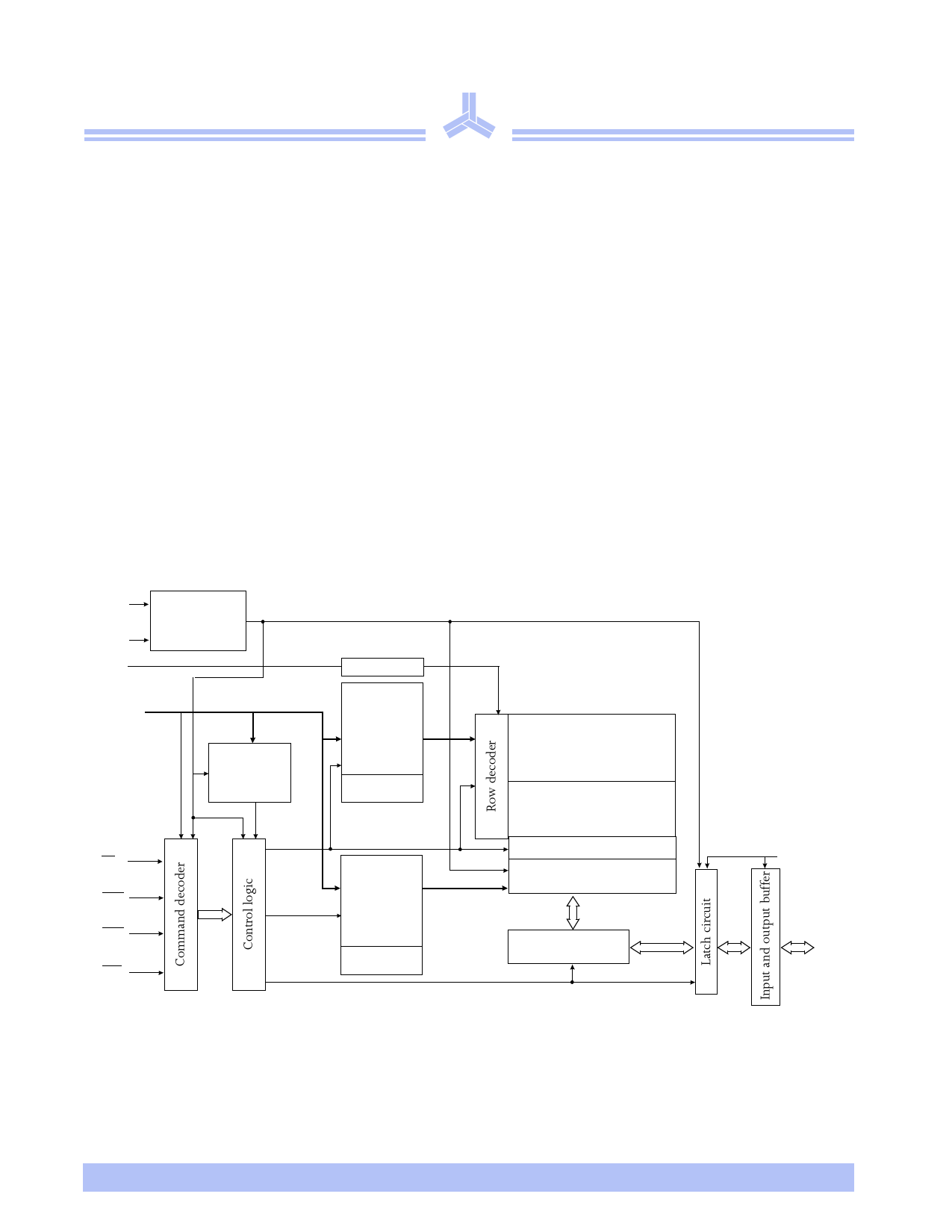

Logic block diagram

CLK

Clock generator

CKE

A11

Bank select

A[10:0]

CS

RAS

CAS

WE

Mode register

Row

address

buffer

Refresh

counter

Column

address

buffer

Burst

counter

Bank Aâ

512K Ă 16 (2048 Ă 256 Ă 16)

Bank Bâ

512K Ă 16 (2048 Ă 256 Ă 16)

Sense amplifier

Column decoder and

latch circuit

Data control circuit

DQMU/DQML

DQ

â For AS4LC2M8S1/AS4LC2M8S0, Banks A and B will read 1M Ă 8 (2048 Ă 512 Ă 8).

5/21/01; v.1.1

Alliance Semiconductor

P. 2 of 29