PEB20320 Ver la hoja de datos (PDF) - Infineon Technologies

Número de pieza

componentes Descripción

Fabricante

PEB20320 Datasheet PDF : 252 Pages

| |||

PEB 20320

Introduction

Pin Definitions and Functions (cont’d)

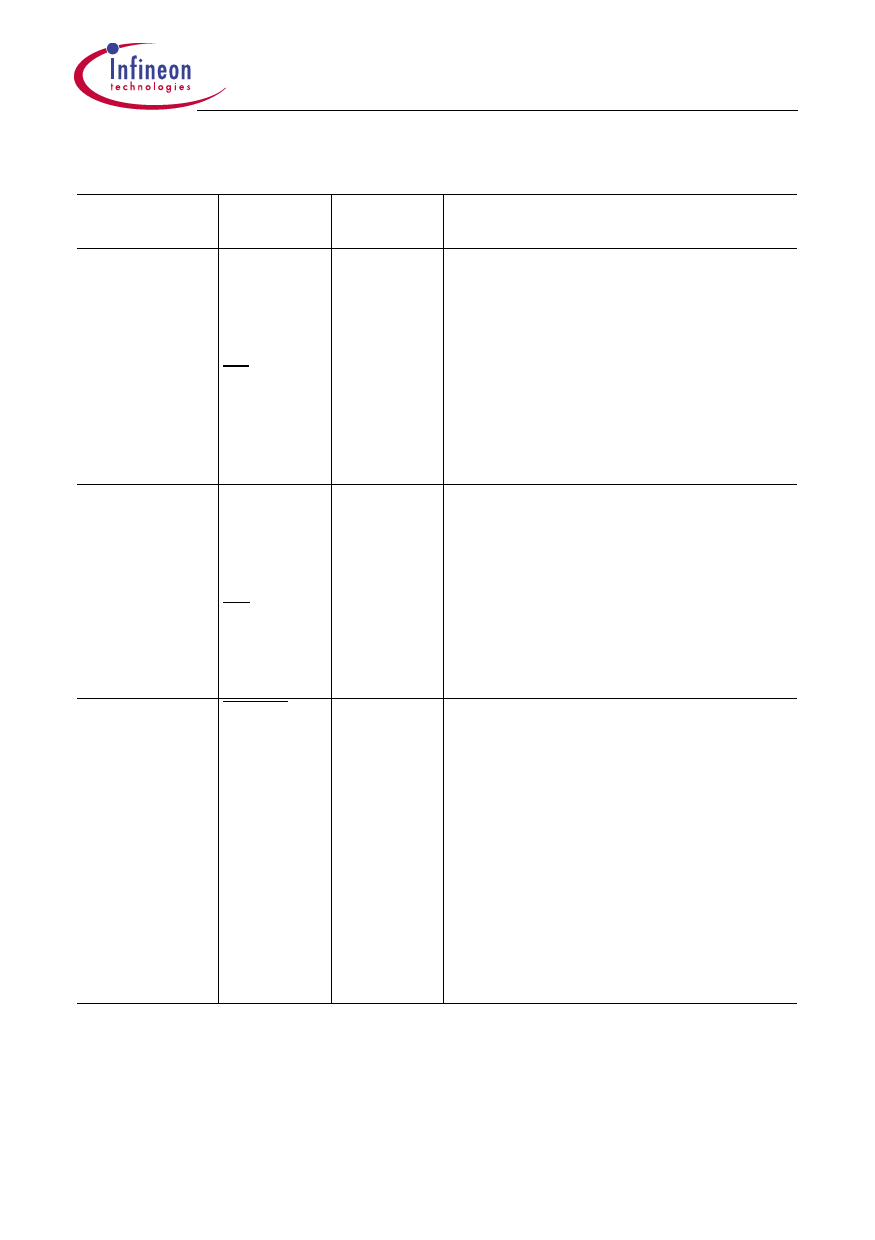

Pin No.

Symbol

P-MQFP-160-1

82

HOLD

Input (I) Function

Output (O)

O

Bus Hold Request (Intel bus mode)

This signal is driven high when the

MUNICH32 requests the control of the

bus.

BR

I/O Bus Request (Motorola bus mode)

This signal is driven low when the

MUNICH32 requests the control of the bus

and is interpreted when another

MUNICH32 wants to be the bus master.

79

HLDA

I

Bus Hold Acknowledge (Intel bus mode)

This active high signal indicates that the

processor has released the control of the

bus. The MUNICH32 starts the bus cycles.

BG

I

Bus Grant (Motorola bus mode)

This active low signal indicates that the

MUNICH32 may assume the bus

mastership.

81

BGACK

I/O Bus Grant Acknowledge (Motorola bus

mode)

This signal is driven low by the device,

when it has become the bus master. It also

informs the MUNICH32 whether another

device is bus master.

PM

I

Parity Mode (Intel bus mode)

This signal has to be strapped to VDD

before reset to enable the Intel parity

mode or to VSS before reset to enable the

Intel non-parity mode. It has to be left

strapped during reset and operation.

User’s Manual

17

01.2000