SP8121 Ver la hoja de datos (PDF) - Signal Processing Technologies

Número de pieza

componentes Descripción

Fabricante

SP8121 Datasheet PDF : 13 Pages

| |||

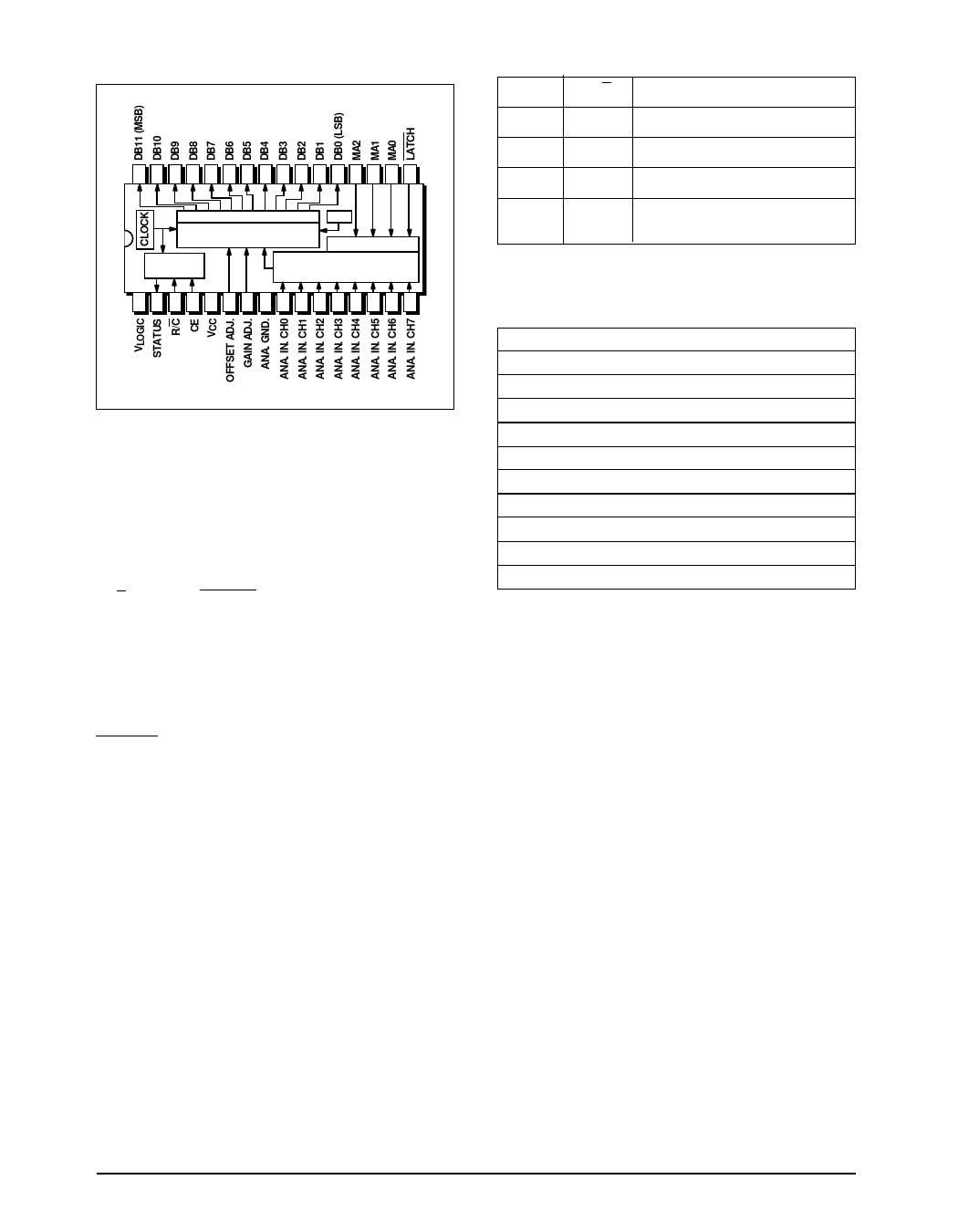

SP8121 PINOUT

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

S

REF

CONTROL

LOGIC

12-BIT ADC

DECODE

8-CHANNEL

MULTIPLEXER

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

SP8121 PINOUT

STATUS — Identifies valid data output; goes to

logic high during conversion; goes to logic low

when conversion is completed and data is valid

R/C — Read/Convert — Initiates conversion on

the high-to-low transition; logic low discon-

nects data bus; logic high initiates read

CE — Chip Enable — Logic low disables read

or convert; logic high enables read or convert

LATCH — MUX Address Latch — Logic high

to low transition captures MUX address on

MUX address lines

MA0, MA1, MA2 — MUX Address 0, 1 & 2 —

Selects analog input channels CH0 through CH7

DB0 through DB11 — Data Outputs — Logic

high is binary true; logic low binary false

SP8121 CONTROL TRUTH TABLE

CE

L->H

1

1

1

R/C

0

0

H ->L

1

OPERATION

Start Conversion

Start Conversion

Start Conversion

Enable 12-bit Output

(when STATUS=0)

SP8121 MULTIPLEXER TRUTH TABLE

LATCH MA2 MA1 MA0 OPERATION

H -> L 0

0

0 CHO Selected

H -> L 0

0

1 CH1 Selected

H -> L 0

1

0 CH2 Selected

H -> L 0

1

1 CH3 Selected

H -> L 1

0

0 CH4 Selected

H -> L 1

0

1 CH5 Selected

H -> L 1

1

0 CH6 Selected

H -> L 1

1

1 CH7 Selected

0

X

X

X Prev. CH “n” Held

1

X

X

X Prev. CH “n” Held

SP8121DS/02

SP8121 Monolithic, 12-Bit Data Acquisition System

4

© Copyright 2000 Sipex Corporation