CL7256S Ver la hoja de datos (PDF) - Clear Logic

Número de pieza

componentes Descripción

Fabricante

CL7256S Datasheet PDF : 16 Pages

| |||

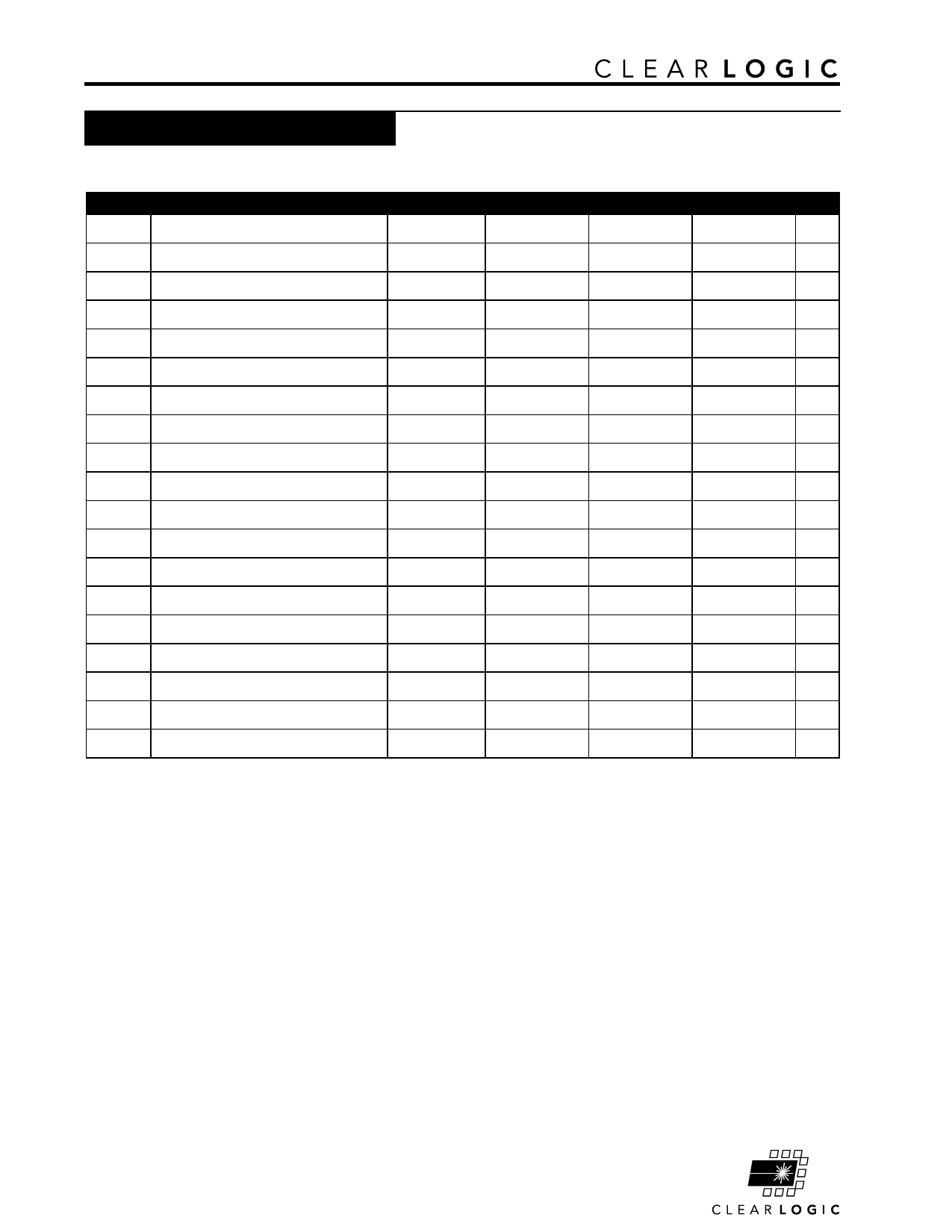

CL7256E and CL7256S Laser Processed Logic Devices

AC Electrical Specifications

I/O Element Timing Parameters [5]

Speed: -6

Symbol

Parameter

Conditions Min Max

tPD1 Input to non-registered output

CL = 35 pF

6.0

tPD2 I/O input to non-registered output

CL = 35 pF

6.0

tSU Global clock setup time

4.2

tH

Global clock hold time

-0.8

tFSU Global clock setup time of fast input

2.5

tFH Global clock hold time of fast input

0.0

tCO1 Global clock to output delay

CL = 35 pF

1.0 3.7

tCH Global clock high time

3.0

tCL Global clock low time

3.0

tASU Array clock setup time

1.9

tAH Array clock hold time

1.5

tACO1 Array clock to output delay

CL = 35 pF

6.0

tACH Array clock high time

3.0

tACL Array clock low time

3.0

tODH Output data hold time after clock

CL = 35 pF

1.0

tCNT Minimum global clock period

6.9

fCNT Max. internal global clock frequency

144.9

tACNT Minimum array clock period

6.9

fACNT Max. internal array clock frequency

144.9

Speed: -7

Min Max

7.5

7.5

3.9

0.0

3.0

0.0

4.7

3.0

3.0

0.8

1.9

7.8

3.0

3.0

1.0

7.8

128.2

7.8

128.2

Speed: -10

Min Max Unit

10.0 ns

10.0 ns

7.0

ns

0.0

ns

3.0

ns

0.5

ns

5.0 ns

4.0

ns

4.0

ns

2.0

ns

3.0

ns

10.0 ns

4.0

ns

4.0

ns

1.0

ns

10.0 ns

100.0

MHz

10.0 ns

100.0

MHz

7K tbl 06E1

Page 8