VV5430 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

VV5430 Datasheet PDF : 33 Pages

| |||

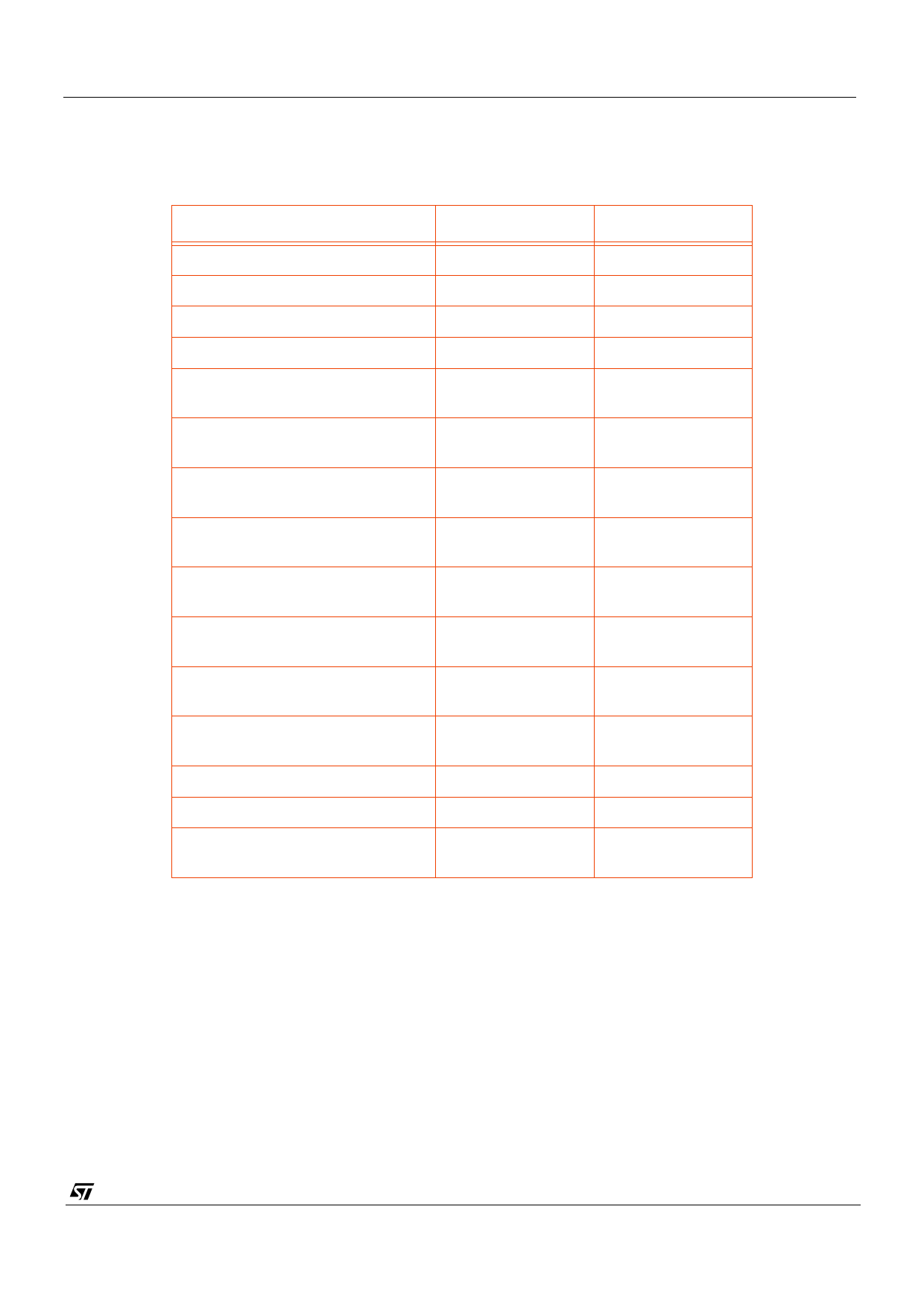

Control Signals for Image Digitisation

5.1 Image Capture Control Signal Timing

The time intervals given are correct for the recommended crystals:

Name

Crystal Frequency (FCKIN)

Pixel clock period (Tpck = 2/FCKIN)

PV (Pixel clock) mark:space

PV high period (Tpv = Tpck/2)

Even (first) field period (Tfield)

Odd (second) field period (Tfield)

FST duration (TFST)

Line period (Tline)

LST duration (TLST)

First visible line delay (Tblank)

First visible pixel delay (Tporch)

Visible line period

Max AVO to PV setup time (Tpsu)

Min. PV to AVO hold time (Tphd)

ODD to FST rise (TODD)

CCIR

14.7456 MHz

135.63 nsec

1:1

67.82 nsec

20.032 msec

(313 x Tline)

19.968 msec

(312 x Tline)

7.73 µsec

(57 x Tpck)

64.0 usec

(472 x Tpck)

4.61 µsec

(34 x Tpck)

704.949 µsec

(11xTline + 7xTpck)

10.58 µsec

(78 x Tpck)

52.083 µsec

(384 x Tpck)

33.9 nsec

30nsec

21.700 msec

(160 x Tpck)

Table 9 : Signal Timing

EIA

12.0000 MHz

166.67nsec

1:1

83.34 nsec

16.7005 msec

(263 x Tline)

16.637 msec

(262 x Tline)

6.1 µsec

(45 x Tpck)

63.5 µsec

(381 x Tpck)

4.66 µsec

(28 x Tpck)

762.833µsec

(12xTline + Tpck)

8.833 µsec

(53 x Tpck)

53.333 µsec

(320 x Tpck)

41.7nsec

40nsec

11.500 msec

(69 x Tpck)

VV5430

CD5430F-A

14/33