APA3160A Ver la hoja de datos (PDF) - Anpec Electronics

Número de pieza

componentes Descripción

Fabricante

APA3160A Datasheet PDF : 38 Pages

| |||

APA3160A

Function Description (Cont.)

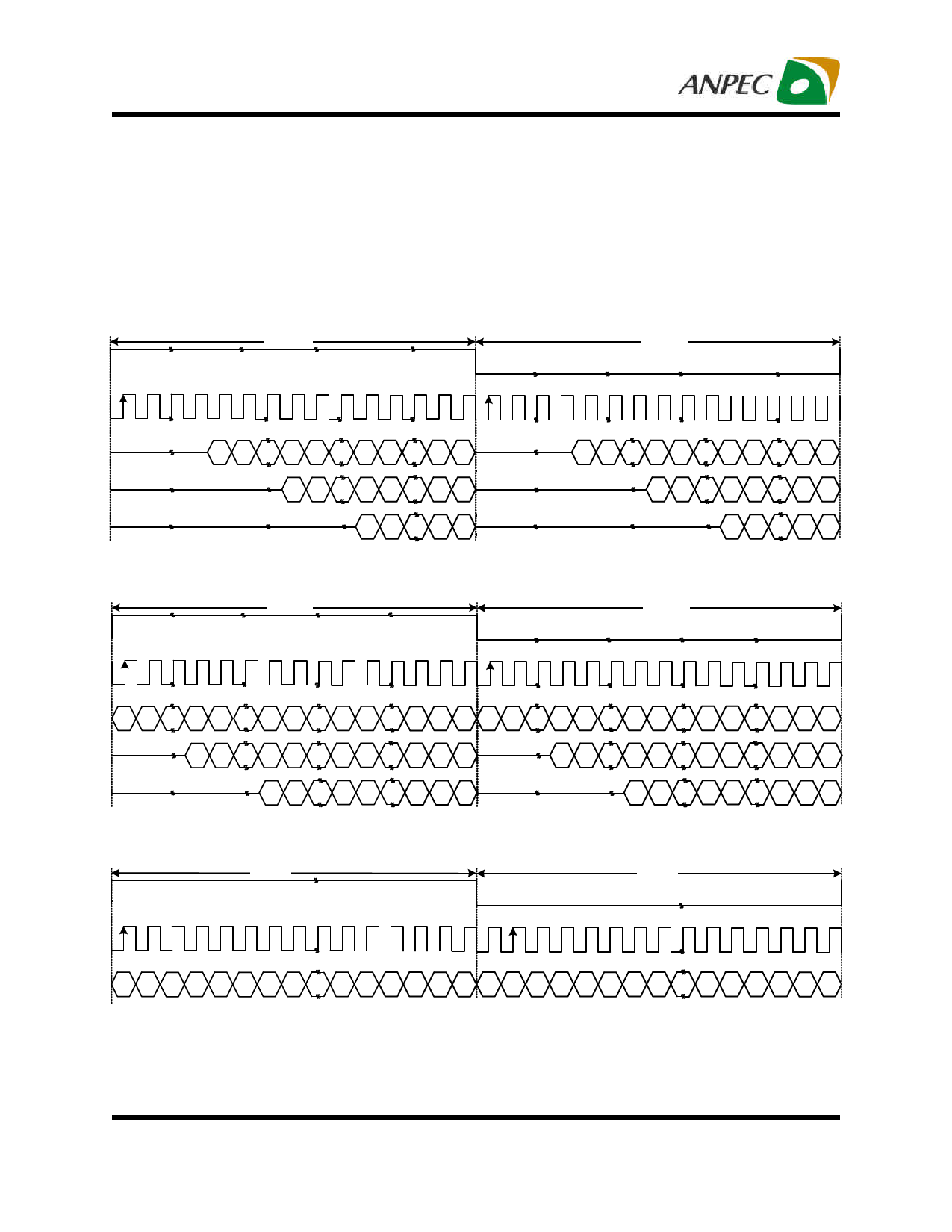

Right-Justified

Right-justified (RJ) timing uses LRCLK to define the data for the left channel and the right channel when the data

being transmitted. For the left channel, the LRCLK is high; for the right channel, the LRCLK low. A bit clock running at

32, 48, or 64 × fS is used to clock in the data. After LRCLK toggles, for 24bit data, the first bit of data appears on the data

8 bit-clock. In RJ mode, the LSB of data is always clocked by the last bit clock before LRCLK transitions. The data is

written MSB first and is valid on the rising edge of bit clock. The DAP masks unused leading data bit positions.

LRCLK

SCLK

32 Clks

Left Channel

SCLK

32 Clks

Right Channel

MSB

24-Bit Mode

20-Bit

Mode

16-Bit

Mode

23 22

19 18

19 18

15 14

15 14

15 14

LSB

10

10

10

MSB

24-Bit Mode

20-Bit

Mode

16-Bit

Mode

23 22

19 18

19 18

15 14

15 14

15 14

LSB

10

10

10

LRCLK

SCLK

24 Clks

Left Channel

Figure 7. Right-Justified 64 f Format

S

SCLK

24 Clks

Right Channel

MSB

24-Bit Mode

23 22

20-Bit

Mode

16-Bit

Mode

19 18

19 18

15 14

15 14

15 14

65

65

65

LS

B

MSB

24-Bit Mode

2 1 0 23 22

19 18

20-Bit

2 1 0 Mode

19 18

16-Bit

Mode

210

15 14

15 14

15 14

65

65

65

LS

B

210

210

210

LRCLK

SCLK

16Clks

Left Channel

Figure 8. Right-Justified 48 f Format

S

SCLK

16Clks

Right Channel

MSB

16-Bit Mode

15 14 13 12 11 10 9 8

LSB MSB

16-Bit Mode

5 4 3 2 1 0 15 14 13 12 11 10 9 8

LSB

543210

Figure 9. Right-Justified 32 fS Format

Copyright © ANPEC Electronics Corp.

14

Rev. A.6 - Jan., 2013

www.anpec.com.tw