HI-5701 Ver la hoja de datos (PDF) - Renesas Electronics

Número de pieza

componentes Descripción

Fabricante

HI-5701 Datasheet PDF : 12 Pages

| |||

HI-5701

Offset Adjustment

The preferred offset correction method is to introduce a DC

component to VIN of the converter. An alternate method is to

adjust the VREF- input to produce the desired offset

adjustment. The theoretical input voltage to produce the first

transition is 1/2 LSB.

VIN (0 to 1 transition) = 1/2 LSB = 1/2(VREF/64) = VREF/128.

Gain Adjustment

In general, full scale error correction can be done in the

preamp circuitry by adjusting the gain of the op amp. An

alternate method is to adjust the VREF+ input voltage. This

adjustment is performed by setting VIN to the 63 to overflow

transition. The theoretical input voltage to produce the transition

is 1/2 LSB less than VREF+ and is calculated as follows:

VIN (63 to 64 transition) = VREF - (VREF/128)

= VREF(127/128).

To perform the gain trim, first do the offset trim and then apply

the required VIN for the 63 to overflow transition. Now adjust

VREF+ until that transition occurs on the outputs.

Midpoint Trim

The reference center (1/2R) is available to the user as the

midpoint of the resistor ladder. The 1/2R point can be used to

improve linearity or create unique transfer functions. The offset

and gain trims should be done prior to adjusting the midpoint.

The theoretical transition from count 31 to 32 occurs at 31.5

LSBs. That voltage is calculated as follows:

VIN (31 to 32 transition) = 31.5(VREF/64) = VREF(63/128).

An adjustable voltage follower can be used to drive the 1/2R

pin. Set VIN to the 31 to 32 transition voltage, then adjust the

voltage follower until the transition occurs on the output bits.

Signal Source

A current pulse is present at the analog input (VIN) at the

beginning of every sample and auto balance period. The

transient current is due to comparator charging and switch

feed through in the capacitor array. It varies with the amplitude

of the analog input and the sampling rate.

The signal source must be capable of recovering from the

transient prior to the end of the sample period to ensure a valid

signal for conversion. Suitable broad band amplifiers or buffers

which exhibit low output impedance and high output drive

include the HFA-0005, HA-5004, HA-5002, and HA-5033.

The signal source may drive above or below the power supply

rails, but should not exceed 0.5V beyond the rails or damage

may occur. Input voltages of -0.5V to +1/2 LSB are converted

to all zeros; input voltages of VREF+ - 1/2 LSB to VDD + 0.5 are

converted to all ones with the Overflow bit set.

Power Supply

The HI-5701 operates nominally from a 5V supply, but will

function from 3V to 6V. The supply should be well regulated

and “clean” of significant noise, especially high frequency

noise. It is recommended that power supply decoupling

capacitors be placed as close to the supply pin as possible. A

combination of 0.01F ceramic and 10F tantalum capacitors

is recommended for this purpose as shown in the test circuit

Figure 13.

Reducing Power Consumption

Power dissipation in the HI-5701 is related to clock frequency

and clock duty cycle. For a fixed 50% clock duty cycle, power

may be reduced by lowering the clock frequency. For a given

conversion frequency, power may be reduced by shortening

the Auto Balance 1 portion of the clock duty cycle.

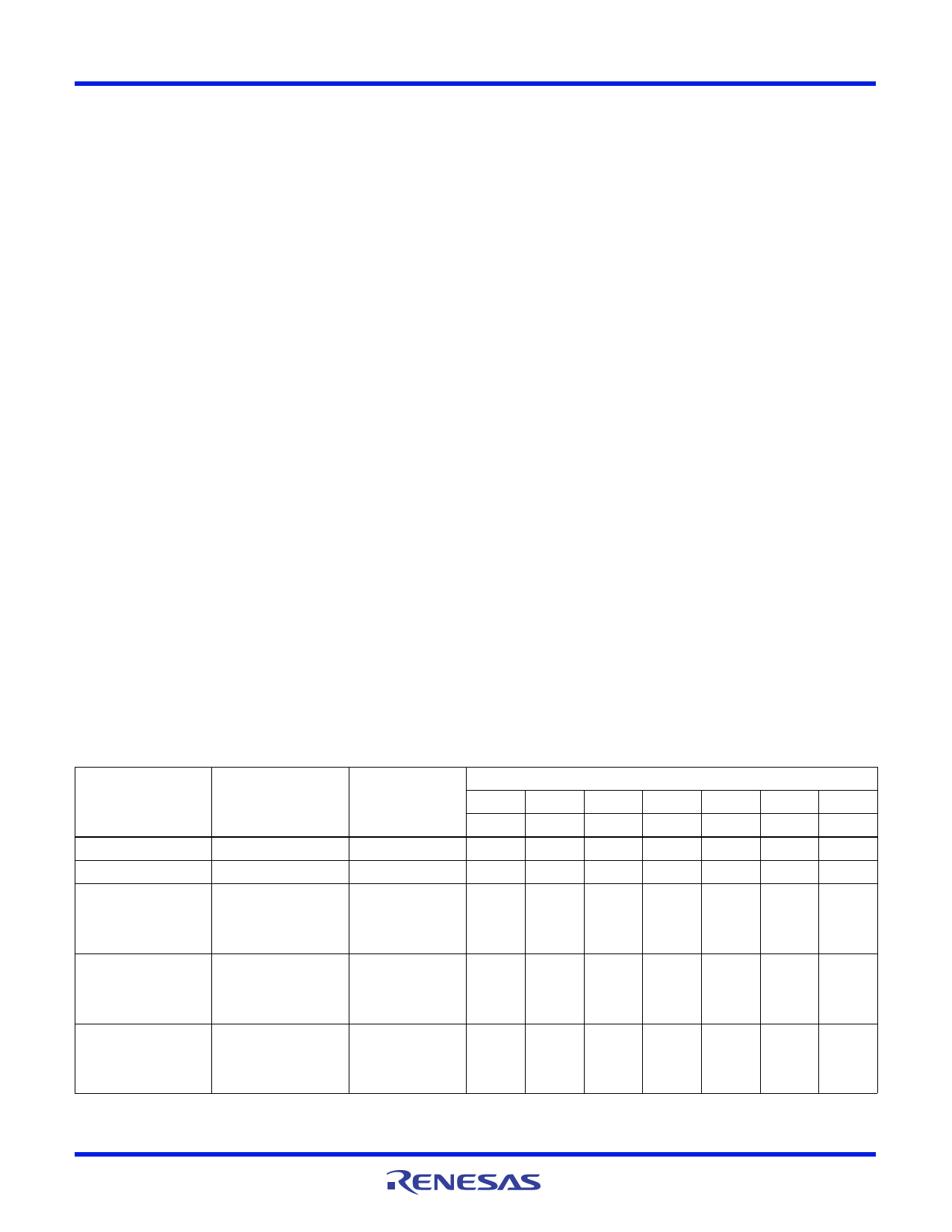

TABLE 4. OUTPUT CODE TABLE

CODE

DESCRIPTION

INPUT VOLTAGE†

VREF+ = 4V

VREF- = 0V

(V)

DECIMAL

COUNT

BINARY OUTPUT CODE

MSB

LSB

OVF

D5

D4

D3

D2

D1

D0

Overflow (OVF)

4.000

127

1

1

1

1

1

1

1

Full Scale (FS)

3.9063

63

0

1

1

1

1

1

1

FS - 1 LSB

3/4 FS

1/2 FS

3.8438

2.9688

1.9688

62

0

1

1

1

1

1

0

48

0

1

1

0

0

0

0

32

0

1

0

0

0

0

0

FN2937 Rev 1.00

September 9, 2005

Page 10 of 12