MA31753 Ver la hoja de datos (PDF) - Dynex Semiconductor

Número de pieza

componentes Descripción

Fabricante

MA31753 Datasheet PDF : 30 Pages

| |||

MA31753

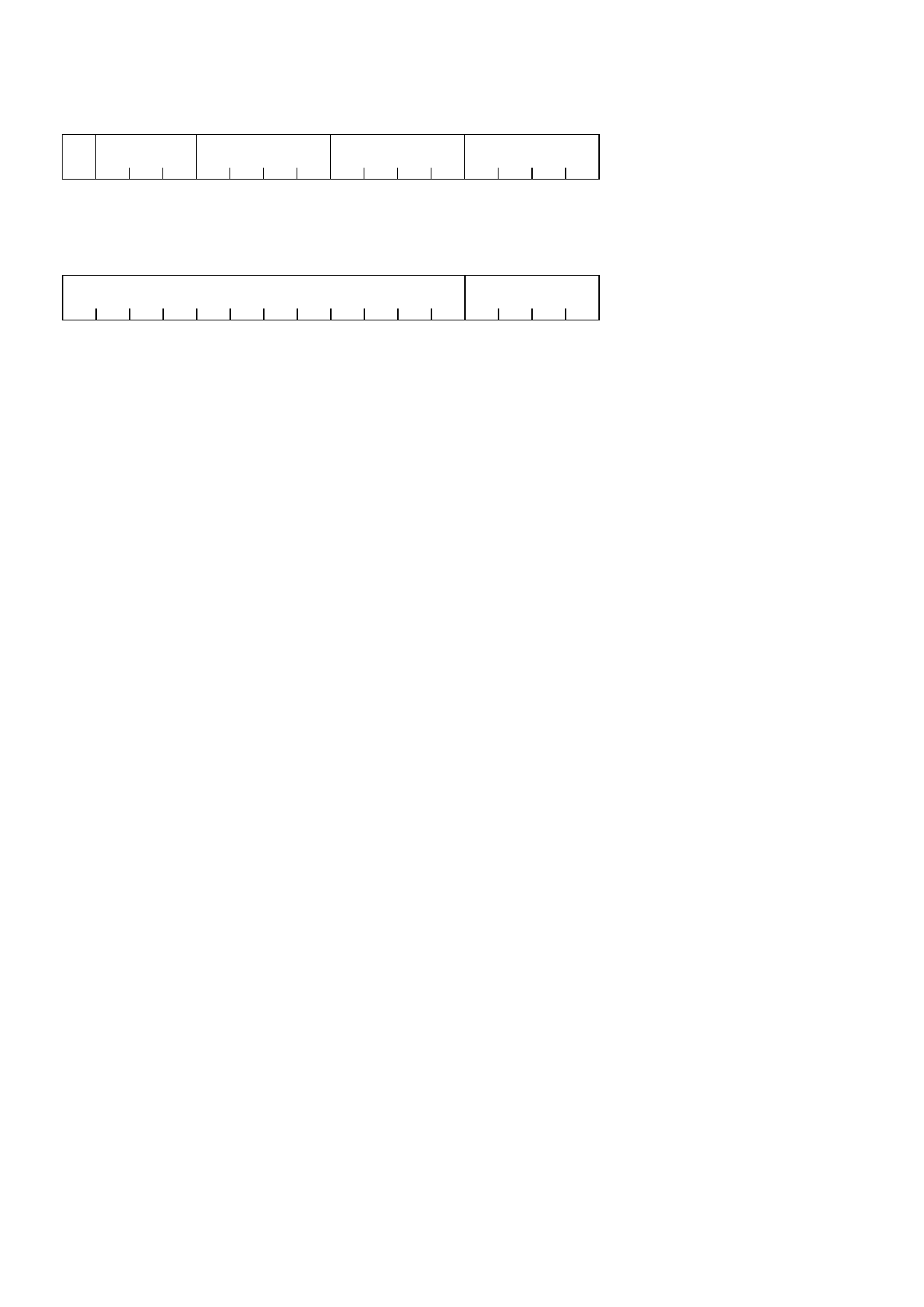

5.4 AREA 1 AND 2 PB, PS AND AS

OIN

PB0

PB3 PS0

PS3 AS0

AS3

D0

D15

These readable and writable registers store the Page Bank, Processor and Address State information to be used when

accessing areas 1 and 2. When areas are defined within IO space, PB, PS and AS are set to zero.

5.5 TRANSFER INTERVAL

Interval

D0

D15

This readable and writable register gives the number of CLK cycles between each DMA request generated during area to

area transfers. The number entered as the interval value corresponds to a clock cycle interval increasing by 32 as follows:

0

=> - (externally triggered DMA requests)

1

=> 0 (continuous DMA requests until the block is completed.

2

=> 32

3

=> 64

4

=> 96

..

..

..

14 => 416

15 => 448

This function is valid only for transfers on channels 0 and 1. Channels 2 and 3 work ony only on externally triggered requests.

5.6 CONFIGURATION WORD

The DMA controller snoops the system address bus for the XIO address 0x8410. When this appears, the DMA stores the data

bus (qualified by DSN low) in an internal copy of the CPU configuration word.

10/30