M38C21F3DXXXFP Ver la hoja de datos (PDF) - MITSUBISHI ELECTRIC

Número de pieza

componentes Descripción

Fabricante

M38C21F3DXXXFP Datasheet PDF : 63 Pages

| |||

PRELIMINARY NSootimcee: pTahriasmisentroict alimfinitsalasrpeescuifbicjeactitotno. change.

MITSUBISHI MICROCOMPUTERS

38C2 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

[Processor Status Register (PS)]

The processor status register is an 8-bit register consisting of 5 flags

which indicate the status of the processor after an arithmetic opera-

tion and 3 flags which decide MCU operation. Branch operations

can be performed by testing the Carry (C) flag , Zero (Z) flag, Over-

flow (V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N

flags are not valid.

• Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic

logic unit (ALU) immediately after an arithmetic operation. It can

also be changed by a shift or rotate instruction.

• Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation

or a data transfer is “0”, and cleared if the result is anything other

than “0”.

• Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt generated

by the BRK instruction.

Interrupts are disabled when the I flag is “1”.

• Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are ex-

ecuted in binary or decimal. Binary arithmetic is executed when

this flag is “0”; decimal arithmetic is executed when it is “1”.

Decimal correction is automatic in decimal mode. Only the ADC

and SBC instructions can be used for decimal arithmetic.

• Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was gener-

ated by the BRK instruction. The BRK flag in the processor status

register is always “0”. When the BRK instruction is used to gener-

ate an interrupt, the processor status register is pushed onto the

stack with the break flag set to “1”.

• Bit 5: Index X mode flag (T)

When the T flag is “0”, arithmetic operations are performed be-

tween accumulator and memory. When the T flag is “1”, direct arith-

metic operations and direct data transfers are enabled between

memory locations.

• Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte of

signed data. It is set if the result exceeds +127 to -128. When the

BIT instruction is executed, bit 6 of the memory location operated

on by the BIT instruction is stored in the overflow flag.

• Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data

transfer is negative. When the BIT instruction is executed, bit 7 of

the memory location operated on by the BIT instruction is stored in

the negative flag.

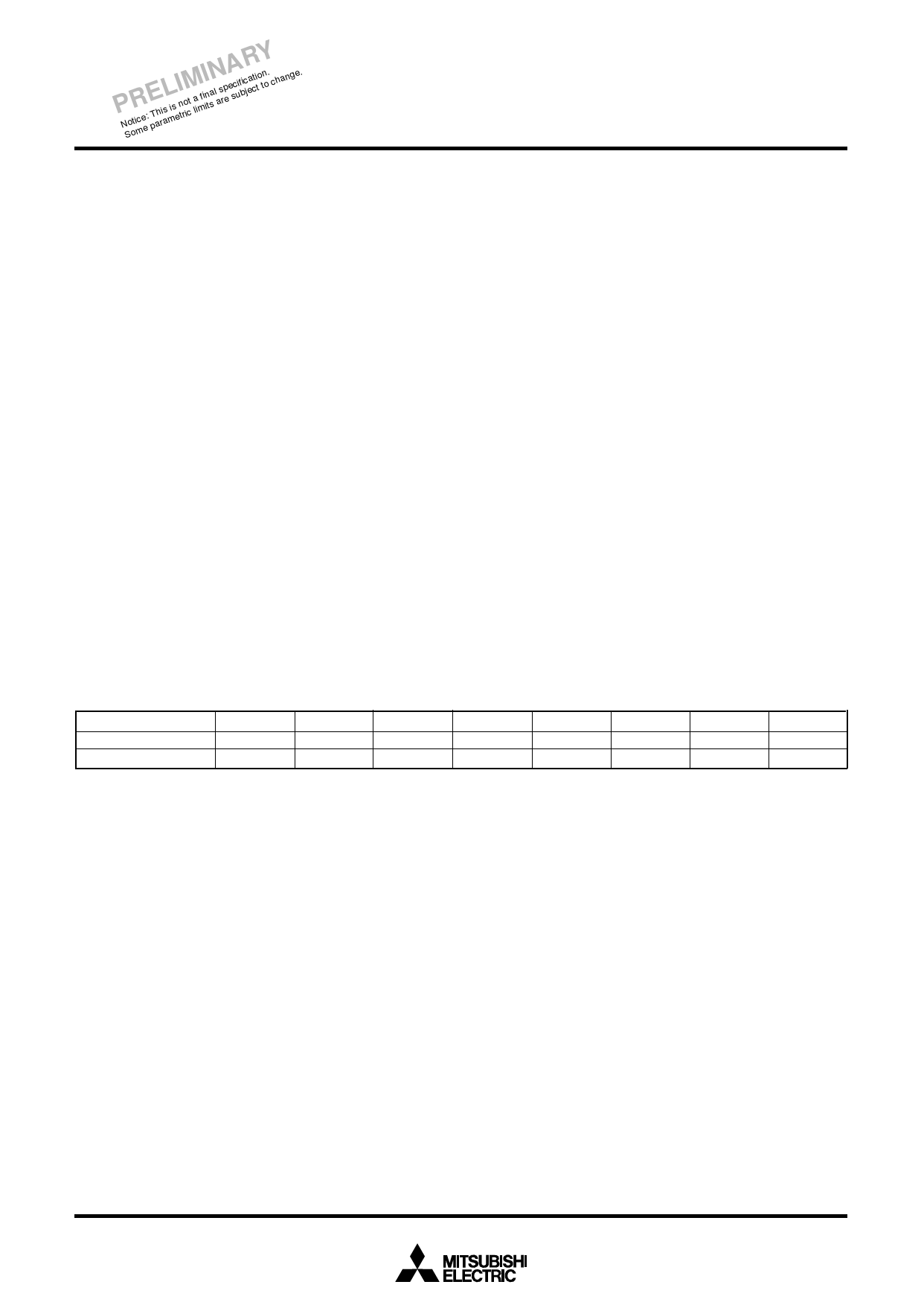

Table 5 Set and clear instructions of each bit of processor status register

Set instruction

Clear instruction

C flag

SEC

CLC

Z flag

–

–

I flag

SEI

CLI

D flag

SED

CLD

B flag

–

–

T flag

SET

CLT

V flag

–

CLV

N flag

–

–

9