KSZ9031RNX(2012) Ver la hoja de datos (PDF) - Micrel

Número de pieza

componentes Descripción

Fabricante

KSZ9031RNX Datasheet PDF : 75 Pages

| |||

Micrel, Inc.

KSZ9031RNX

• Write value 0x03FF (delay GTX_CLK and RX_CLK pad skews to their maximum values) to MMD Address 2h,

register 8h

- Write register 0xD = 0x0002 // Select MMD Device Address 2h

- Write register 0xE = 0x0008 // Select register 8h of MMD Device Address 2h

- Write register 0xD = 0x4002 // Select register data for MMD Device Address 2h, register 8h

- Write register 0xE = 0x03FF // Write value 0x03FF to MMD Device Address 2h, register 8h

RGMII In-Band Status

The KSZ9031RNX provides in-band status to the MAC during the inter-frame gap when RX_DV is de-asserted. RGMII in-

band status is always enabled after power-up.

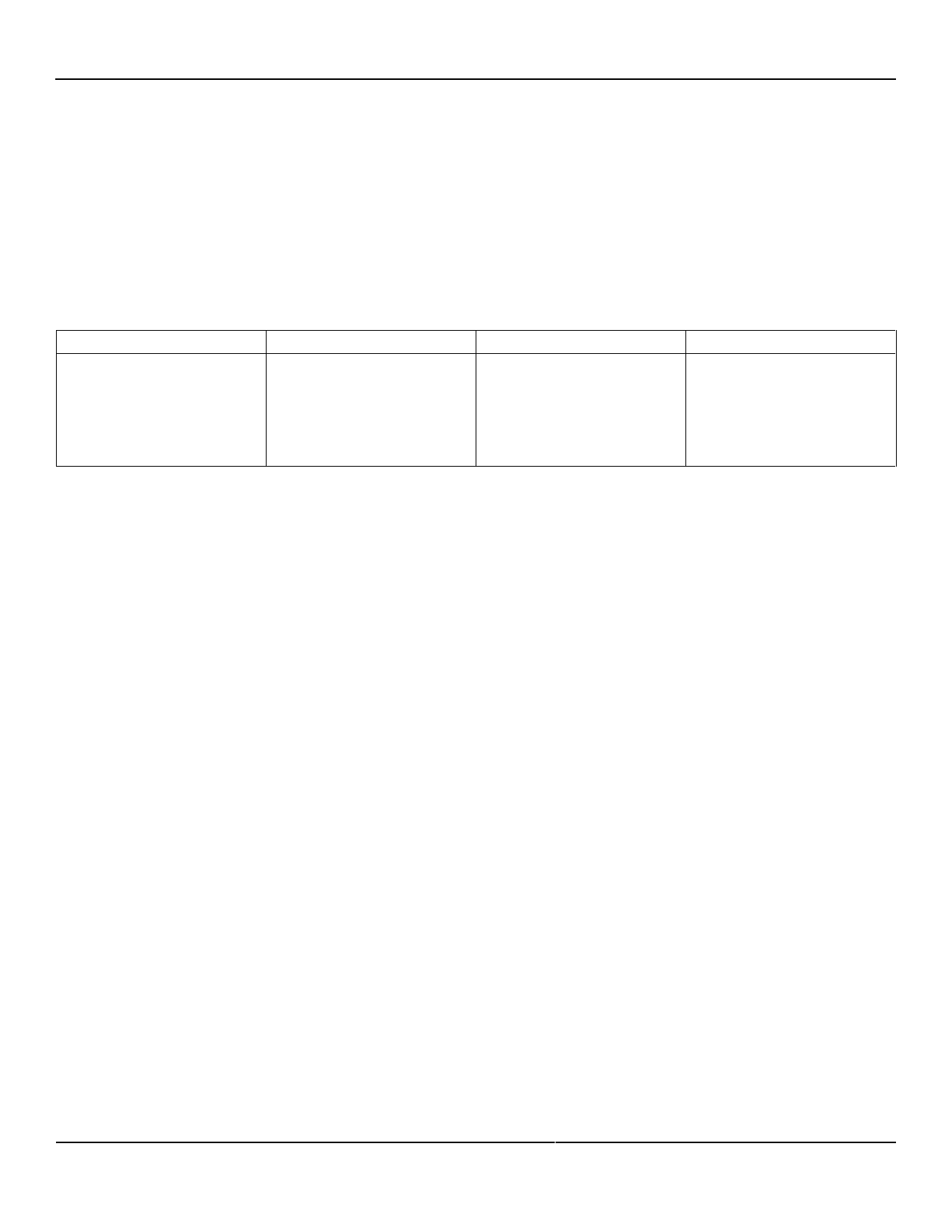

The in-band status is sent to the MAC using the RXD[3:0] data pins, and is described in Table 7.

RX_DV

0

(valid only when RX_DV

is low)

RXD3

Duplex Status

0 = Half-duplex

1 = Full-duplex

RXD[2:1]

RX_CLK clock speed

00 = 2.5MHz (10Mbps)

01 = 25MHz (100Mbps)

10 = 125MHz (1000Mbps)

11 = Reserved

RXD0

Link Status

0 = Link down

1 = Link up

Table 7. RGMII In-Band Status

MII Management (MIIM) Interface

The KSZ9031RNX supports the IEEE 802.3 MII Management interface, also known as the Management Data Input/

Output (MDIO) interface. This interface allows upper-layer devices to monitor and control the state of the KSZ9031RNX.

An external device with MIIM capability is used to read the PHY status and/or configure the PHY settings. More details

about the MIIM interface can be found in Clause 22.2.4 of the IEEE 802.3 Specification.

The MIIM interface consists of the following:

• A physical connection that incorporates the clock line (MDC) and the data line (MDIO).

• A specific protocol that operates across the physical connection mentioned earlier, which allows an external

controller to communicate with one or more KSZ9031RNX devices. Each KSZ9031RNX device is assigned a

unique PHY address between 0h and 7h by the PHYAD[2:0] strapping pins.

• A 32-register address space for direct access to IEEE-defined registers and vendor-specific registers, and for

indirect access to MMD addresses and registers. See the “Register Map” section.

PHY address 0h is supported as the unique PHY address only; it is not supported as the broadcast PHY address, which

allows for a single write command to simultaneously program an identical PHY register for two or more PHY devices (for

example, using PHY address 0h to set register 0h to a value of 0x1940 to set bit [11] to a value of one to enable software

power-down). Instead, separate write commands are used to program each PHY device.

Table 8 shows the MII Management frame format for the KSZ9031RNX.

Preamble

Read 32 1’s

Write 32 1’s

Start of

Frame

01

01

Read/Write

OP Code

10

01

PHY

Address

Bits [4:0]

00AAA

00AAA

REG

Address

Bits [4:0]

RRRRR

RRRRR

TA

Data

Bits [15:0]

Idle

Z0 DDDDDDDD_DDDDDDDD Z

10 DDDDDDDD_DDDDDDDD Z

Table 8. MII Management Frame Format for the KSZ9031RNX

October 2012

27

M9999-103112-1.0