IDT5P49V5901 Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Fabricante

IDT5P49V5901 Datasheet PDF : 35 Pages

| |||

IDT5P49V5901

PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

OTP Interface

The IDT5P49V5901 can also store its configuration in an

internal OTP. The contents of the device's internal

programming registers can be saved to the OTP by setting

burn_start (W114[3]) to high and can be loaded back to the

internal programming registers by setting

usr_rd_start(W114[0]) to high.

To initiate a save or restore using I2C, only two bytes are

transferred. The Device Address is issued with the

read/write bit set to “0”, followed by the appropriate

command code. The save or restore instruction executes

after the STOP condition is issued by the Master, during

which time the IDT5P49V5901 will not generate

Acknowledge bits. The IDT5P49V5901 will acknowledge

the instructions after it has completed execution of them.

During that time, the I2C bus should be interpreted as busy

by all other users of the bus.

On power-up of the IDT5P49V5901, an automatic restore is

performed to load the OTP contents into the internal

programming registers. The IDT5P49V5901 will be ready to

accept a programming instruction once it acknowledges its

7-bit I2C address.

Availability of Primary and Secondary I2C addresses to

allow programming for multiple devices in a system. The I2C

slave address can be changed from the default 0xD4 to

0xD0 by programming the I2C_ADDR bit D0. VersaClock 5

Programming Guide provides detailed I2C programming

guidelines and register map.

SD/OE Pin Function

The polarity of the SD/OE signal pin can be programmed to

be either active HIGH or LOW with the SP bit (W16[1]).

When SP is “0” (default), the pin becomes active LOW and

when SP is “1”, the pin becomes active HIGH. The SD/OE

pin can be configured as either to shutdown the PLL or to

enable/disable the outputs. The SH bit controls the

configuration of the SD/OE pin The SH bit needs to be high

for SD/OE pin to be configured as SD.

When configured as SD, device is shut down, differential

outputs are driven High/low, and the single-ended LVCMOS

outputs are driven low. When configured as OE, and outputs

are disabled, the outputs are driven high/low.

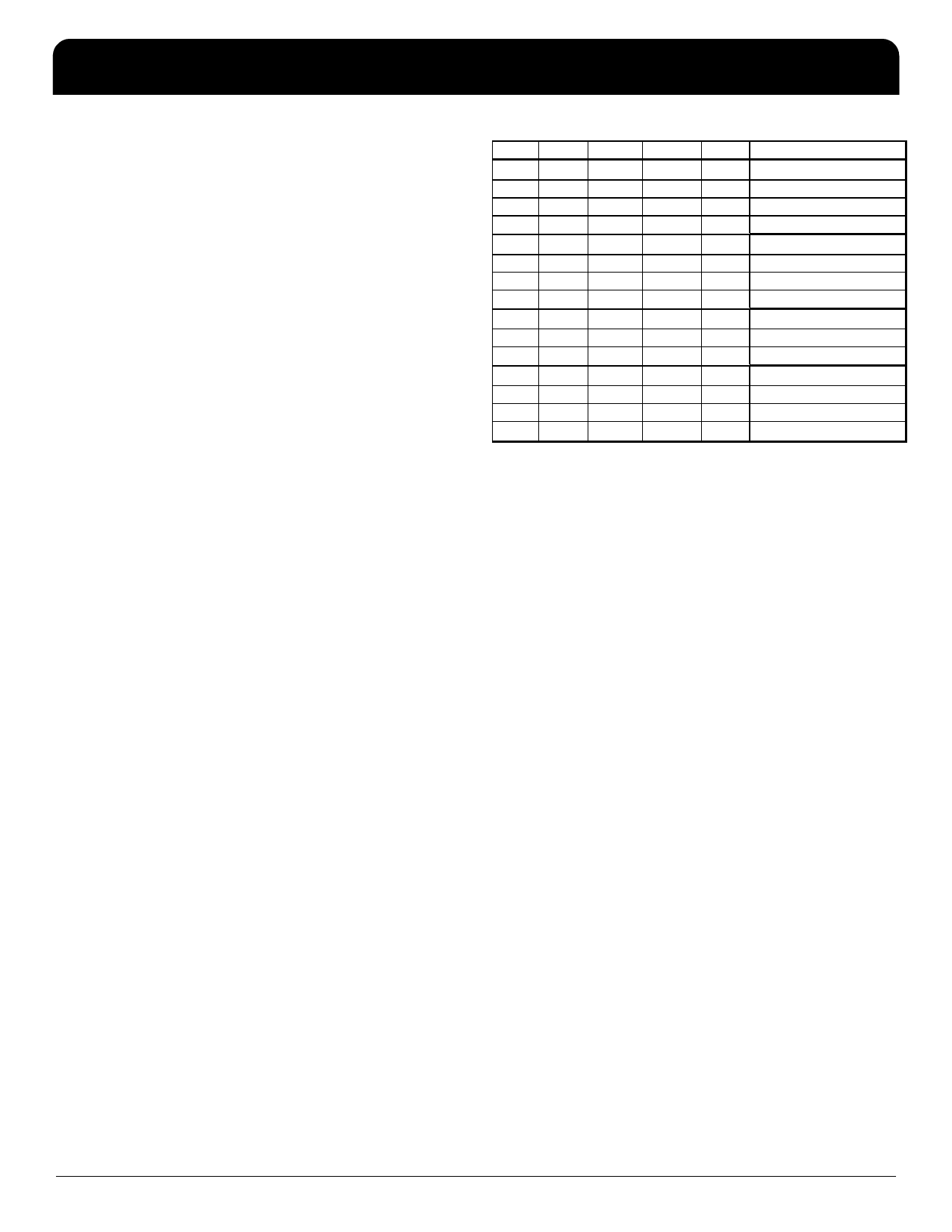

Table 5: SD/OE Pin Function Truth Table

SH bit SP bit OSn bit OEn bit SD/OE

OUTn

0

0

0

x

x Tri-state2

0

0

1

0

x Output active

0

0

1

1

0 Output active

0

0

1

1

1 Output driven High Low

0

1

0

x

x Tri-state2

0

1

1

0

x Output active

0

1

1

1

0 Output driven High Low

0

1

1

1

1 Output active

1

0

0

x

0 Tri-state2

1

0

1

0

0 Output active

1

0

1

1

0 Output active

1

1

0

x

0 Tri-state2

1

1

1

0

0 Output active

1

1

1

1

0 Output driven High Low

1

x

x

x

1 Output driven High Low 1

Note 1 : Global Shutdown

Note 2 : Tri-state regardless of OEn bits

Output Divides

Each output divide block has a synchronizing POR pulse to

provide startup alignment between outputs divides. This

allows alignment of outputs for low skew performance. This

low skew would also be realized between outputs that are

both integer divides from the VCO frequency. This phase

alignment works when using configuration with SEL1,

SEL0. For I2C programming, I2C reset is required.

An output divide bypass mode (divide by 1) will also be

provided, to allow multiple buffered reference outputs.

Each of the four output divides are comprised of a 12 bit

integer counter, and a 24 bit fractional counter. The output

divide can operate in integer divide only mode for improved

performance, or utilize the fractional counters to generate a

clock frequency accurate to 50 ppb.

Each of the output divides also have structures capable of

independently generating spread spectrum modulation on

the frequency output.

The Output Divide also has the capability to apply a spread

modulation to the output frequency. Independent of output

frequency, a triangle wave modulation between 30 and

63kHz may be generated.

For all outputs, there is a bypass mode, to allow the output

to behave as a buffered copy of the input.

IDT® PROGRAMMABLE CLOCK GENERATOR

6

IDT5P49V5901

REV A 031014