74LVX00 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

74LVX00 Datasheet PDF : 8 Pages

| |||

74LVX00

LOW VOLTAGE CMOS QUAD 2-INPUT NAND GATE

WITH 5V TOLERANT INPUTS

s HIGH SPEED :

tPD = 4.1ns (TYP.) at VCC = 3.3V

s 5V TOLERANT INPUTS

s INPUT VOLTAGE LEVEL :

VIL=0.8V, VIH=2V at VCC=3V

s LOW POWER DISSIPATION:

ICC = 2 µA (MAX.) at TA=25°C

s LOW NOISE:

VOLP = 0.3V (TYP.) at VCC = 3.3V

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s OPERATING VOLTAGE RANGE:

VCC(OPR) = 2V to 3.6V (1.2V Data Retention)

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 00

s IMPROVED LATCH-UP IMMUNITY

s POWER DOWN PROTECTION ON INPUTS

DESCRIPTION

The 74LVX00 is a low voltage CMOS QUAD

2-INPUT NAND GATE fabricated with sub-micron

silicon gate and double-layer metal wiring C2MOS

technology. It is ideal for low power, battery

operated and low noise 3.3V applications.

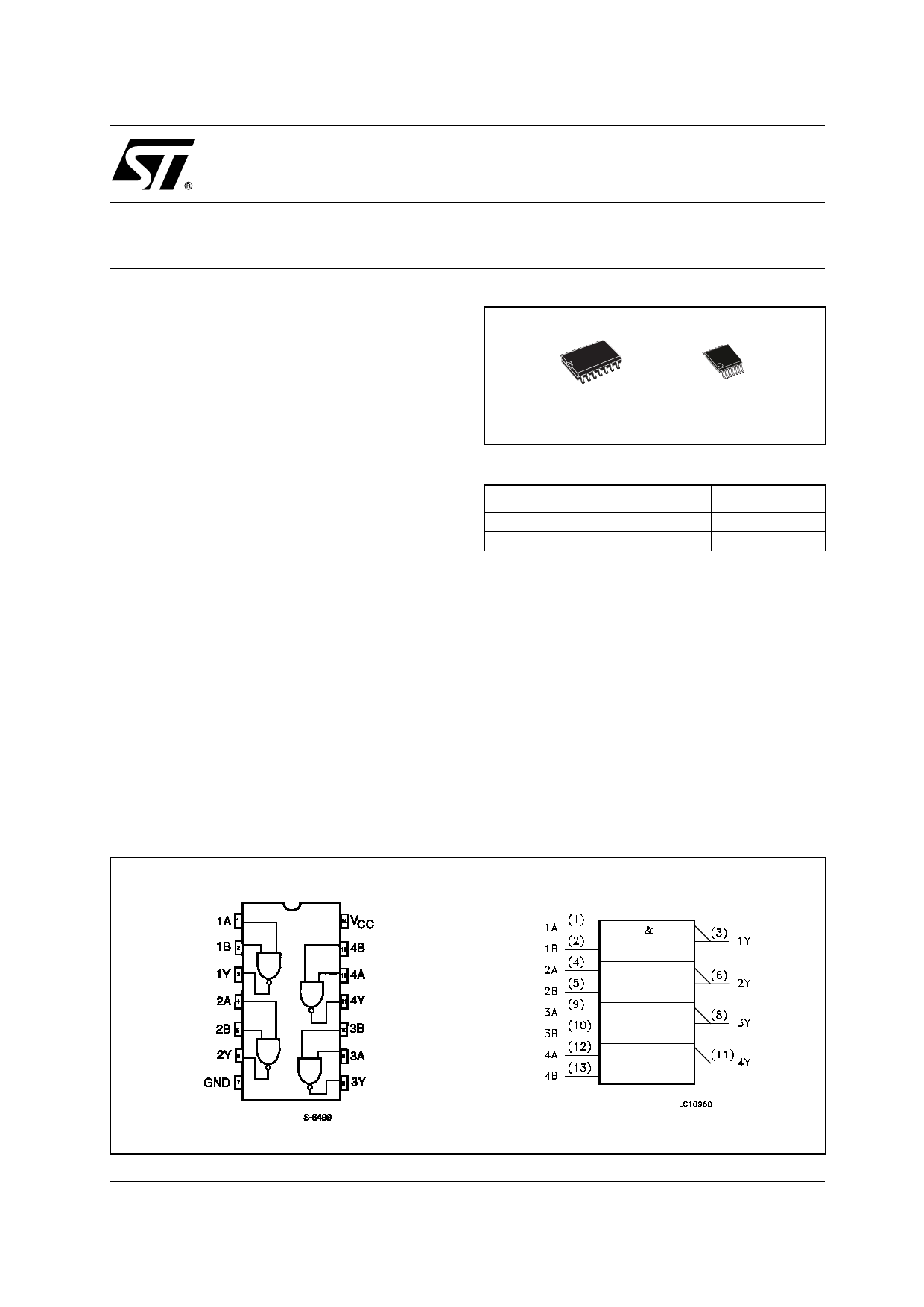

SOP

TSSOP

ORDER CODES

PACKAGE

SOP

TSSOP

TUBE

74LVX00M

T&R

74LVX00MTR

74LVX00TTR

The internal circuit is composed of 3 stages

including buffer output, which provides high noise

immunity and stable output.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage.

This device can be used to interface 5V to 3V

system. It combines high speed performance with

the true CMOS low power consumption. All inputs

and outputs are equipped with protection circuits

against static discharge, giving them 2KV ESD

immunity and transient excess voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

July 2001

1/8