74LCXR162245 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

74LCXR162245

74LCXR162245 Datasheet PDF : 10 Pages

| |||

74LCXR162245

LOW VOLTAGE CMOS 16-BIT BUS TRANSCEIVER

WITH 5V TOLERANT INPUTS AND OUTPUT (3-STATE)

s 5V TOLERANT INPUTS AND OUTPUTS

s HIGH SPEED :

tPD = 4.2 ns (MAX.) at VCC = 3V

s POWER DOWN PROTECTION ON INPUTS

AND OUTPUTS

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 12mA (MIN) at VCC = 3V

s PCI BUS LEVELS GUARANTEED AT 12 mA

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s OPERATING VOLTAGE RANGE:

VCC(OPR) = 2.0V to 3.6V (1.5V Data

Retention)

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 16245

s LATCH-UP PERFORMANCE EXCEEDS

500mA (JESD 17)

s ESD PERFORMANCE:

HBM > 2000V (MIL STD 883 method 3015);

MM > 200V

DESCRIPTION

The 74LCXR162245 is a low voltage CMOS 16

BIT BUS TRANSCEIVER (3-STATE) fabricated

with sub-micron silicon gate and double-layer

metal wiring C2MOS technology. It is ideal for low

power and high speed 3.3V applications; it can be

interfaced to 5V signal environment for both inputs

and outputs.

This IC is intended for two-way asynchronous

communication between data buses; the direction

of data transmission is determined by DIR input.

The two enable inputs nG can be used to disable

the device so that the buses are effectively isolat-

ed.

All outputs, wich are designed to sink up to 12mA,

include 26Ω resistors to reduce overshoot and un-

dershoot.

All inputs and outputs are equipped with protec-

tion circuits against static discharge, giving them

2KV ESD immunity and transient excess voltage.

All floating bus terminals during High Z State must

be held HIGH or LOW.

TSSOP

ORDER CODES

PACKAGE

TSSOP

TUBE

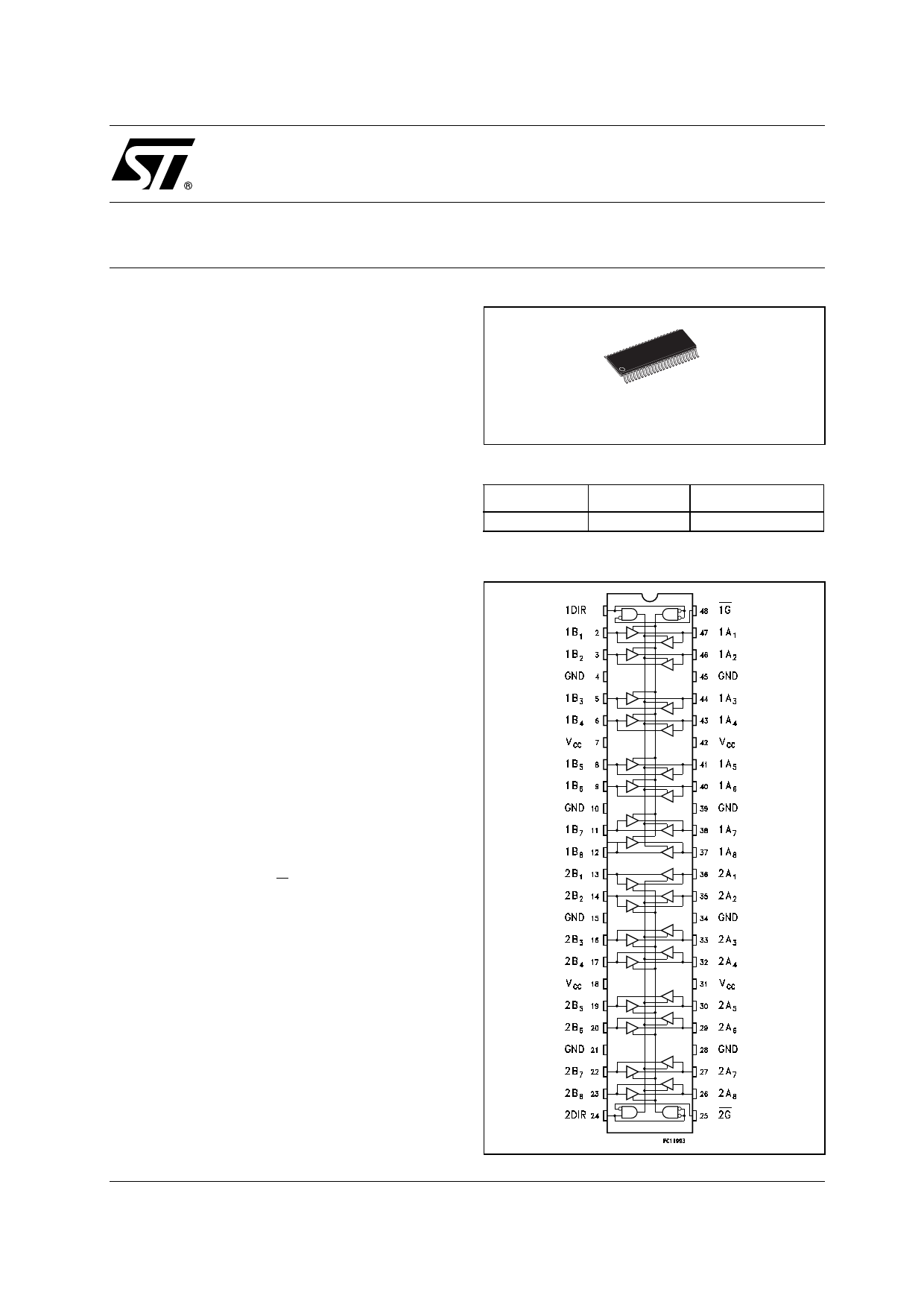

PIN CONNECTION

T&R

74LCXR162245TTR

February 2003

1/10