DP8051CPU Ver la hoja de datos (PDF) - Digital Core Design

Número de pieza

componentes Descripción

Fabricante

DP8051CPU Datasheet PDF : 9 Pages

| |||

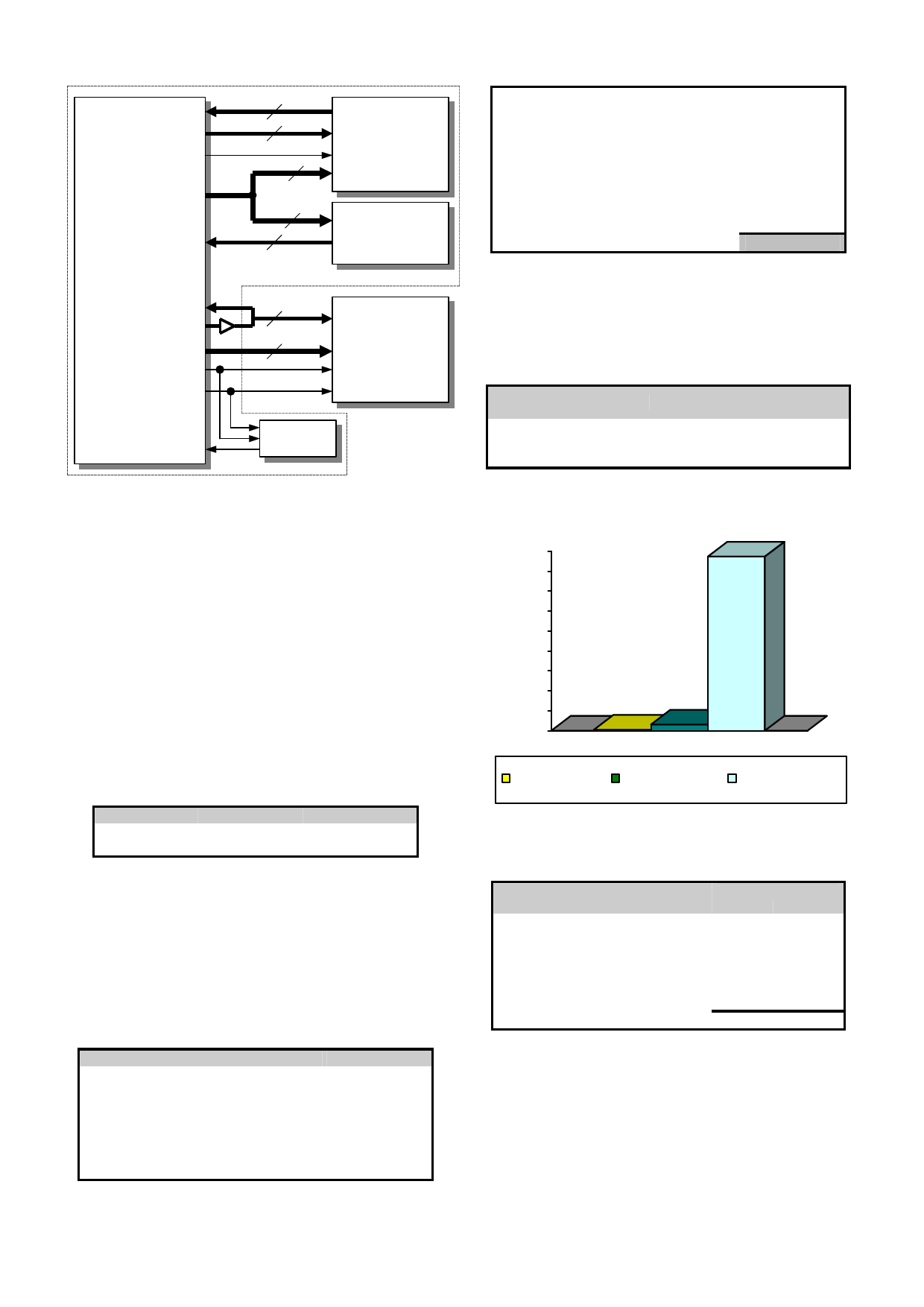

prgramdatai

prgdatao

prgramwr

prgaddr

prgromdata

DP8051 i

xdatai

xdatao

xaddr

xprgrd

xprgwr

8

8

12

On-chip Memory

(implemented as RAM)

0 Wait-State access

10

8

ASIC or FPGA

chip

On-chip Memory

(implemented as ROM)

0 Wait-State access

8

Off-chip Memory

16

(implemented as

FLASH, or SRAM)

eg. 2-5 Wait-State

access

ready

Wait-States

manager

The described above implementation should be

treated as an example. All Program Memory

spaces are fully configurable. For timing-critical

applications whole program code can be imple-

mented as on-chip ROM and (or) RAM and

executed without Wait-States, but for some

other applications whole program code can be

implemented as off-chip ROM or FLASH and

executed with required number Wait-State cy-

cles.

PERFORMANCE

The following tables give a survey about the

Core area and performance in ASICs Devices

(CPU features and peripherals have been in-

cluded):

Device

Optimization

0.25u typical

area

Fmax

100 MHz

0.25u typical

speed

250 MHz

Core performance in ASIC devices

For a user the most important is application

speed improvement. The most commonly used

arithmetic functions and theirs improvement

are shown in table below. Improvement was

computed as {80C51 clock periods} divided by

{DP8051 clock periods} required to execute an

identical function. More details are available in

core documentation.

Function

8-bit addition (immediate data)

8-bit addition (direct addressing)

8-bit addition (indirect addressing)

8-bit addition (register addressing)

8-bit subtraction (immediate data)

8-bit subtraction (direct addressing)

8-bit subtraction (indirect addressing)

Improvement

9,00

9,00

9,00

12,00

9,00

9,00

9,00

All trademarks mentioned in this document

are trademarks of their respective owners.

8-bit subtraction (register addressing)

8-bit multiplication

8-bit division

16-bit addition

16-bit subtraction

16-bit multiplication

32-bit addition

32-bit subtraction

32-bit multiplication

Average speed improvement:

12,00

16,00

9,60

12,00

12,00

13,60

12,00

12,00

12,60

11,12

Dhrystone Benchmark Version 2.1 was used to

measure Core performance. The following ta-

ble gives a survey about the DP8051 perform-

ance in terms of Dhrystone/sec and VAX MIPS

rating.

Device

Target

Clock

Dhry/sec

frequency (VAX MIPS)

80C51

-

12 MHz

268 (0.153)

80C310

-

33 MHz 1550 (0.882)

DP8051

0.25u

250 MHz 43700 (24.872)

Core performance in terms of Dhrystones

45000

40000

35000

30000

25000

20000

15000

10000

5000

0

43700

268 1550

80C51 (12MHz) 80C310 (33MHz) DP8051 (250MHz)

Area utilized by the each unit of DP8051 core

in vendor specific technologies is summarized

in table below.

CPU*

Component

Area

[Gates]

[FFs]

5900

285

Interrupt Controller

450

40

Power Management Unit

50

5

I/O ports

400

35

Timers

550

50

UART0

650

60

Total area

8000

475

*CPU – consisted of ALU, Opcode Decoder, Control Unit, Program &

Internal & External Memory Interfaces, User SFRs Interface

Core components area utilization

http://www.DigitalCoreDesign.com

http://www.dcd.pl

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.