FM24CL64B(2014) Ver la hoja de datos (PDF) - Cypress Semiconductor

NГәmero de pieza

componentes DescripciГіn

Fabricante

FM24CL64B Datasheet PDF : 19 Pages

| |||

FM24CL64B

full pagewidth

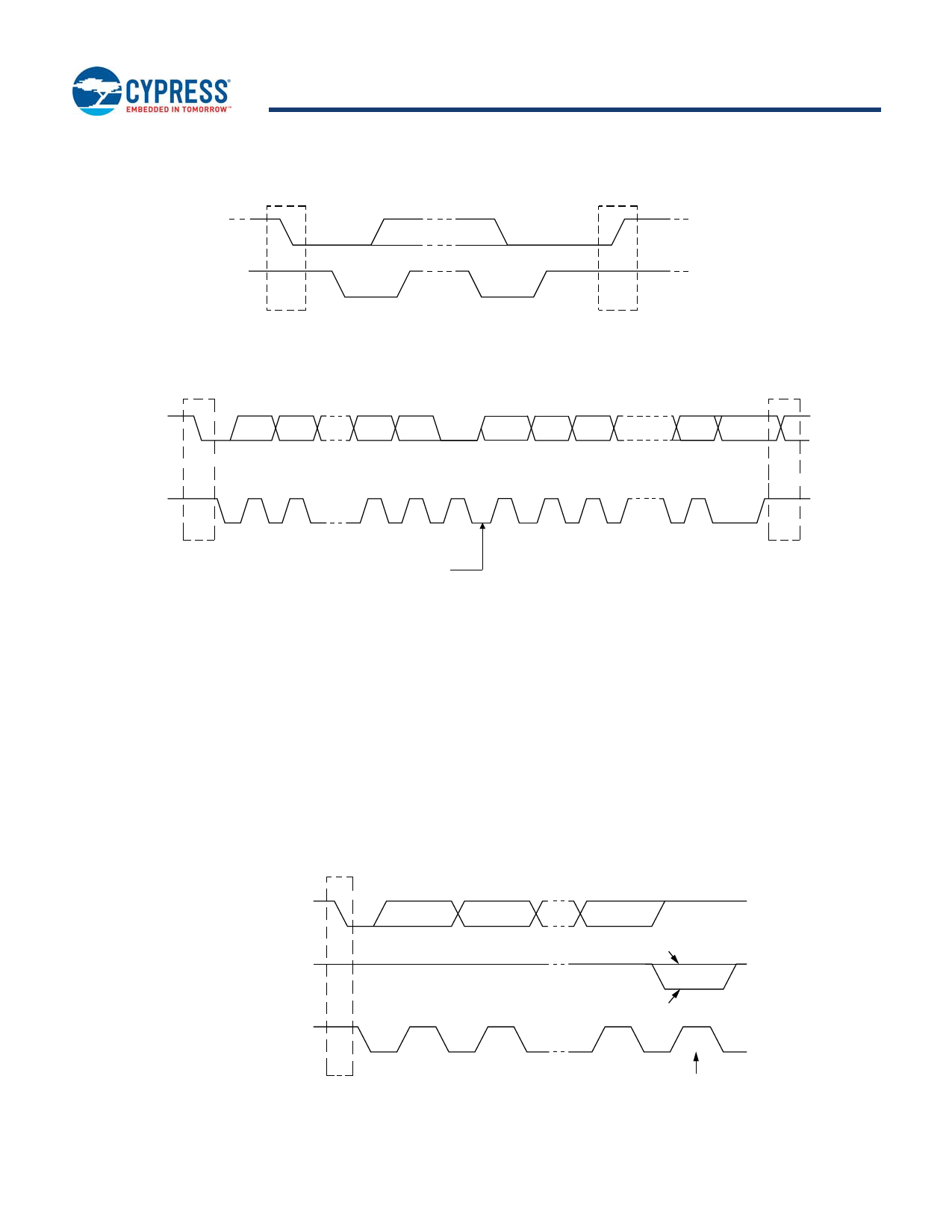

SDA

Figure 4. START and STOP Conditions

SDA

SCL

S

START Condition

SCL

P

STOP Condition

handbook, full pagewidth

SDA

MSB

Figure 5. Data Transfer on the I2C Bus

Acknowledgement

signal from slave

P

Acknowledgement S

signal from receiver

SCL

S

1

2

START

condition

7

8

9

1

ACK

Byte complete

2

3

4-8

9

ACK

S

or

P

STOP or

START

condition

Data/Address Transfer

All data transfers (including addresses) take place while the SCL

signal is HIGH. Except under the three conditions described

above, the SDA signal should not change while SCL is HIGH.

Acknowledge / No-acknowledge

The acknowledge takes place after the 8th data bit has been

transferred in any transaction. During this state the transmitter

should release the SDA bus to allow the receiver to drive it. The

receiver drives the SDA signal LOW to acknowledge receipt of

the byte. If the receiver does not drive SDA LOW, the condition

is a no-acknowledge and the operation is aborted.

The receiver would fail to acknowledge for two distinct reasons.

First is that a byte transfer fails. In this case, the no-acknowledge

ceases the current operation so that the device can be

addressed again. This allows the last byte to be recovered in the

event of a communication error.

Second and most common, the receiver does not acknowledge

to deliberately end an operation. For example, during a read

operation, the FM24CL64B will continue to place data onto the

bus as long as the receiver sends acknowledges (and clocks).

When a read operation is complete and no more data is needed,

the receiver must not acknowledge the last byte. If the receiver

acknowledges the last byte, this will cause the FM24CL64B to

attempt to drive the bus on the next clock while the master is

sending a new command such as STOP.

Figure 6. Acknowledge on the I2C Bus

handbook, full pagewidth

DATA OUTPUT

BY MASTER

DATA OUTPUT

BY SLAVE

No Acknowledge

Acknowledge

SCL FROM

MASTER

S

1

2

START

Condition

8

9

Clock pulse for

acknowledgement

Document Number: 001-84458 Rev. *D

Page 5 of 19