A6259KA Ver la hoja de datos (PDF) - Allegro MicroSystems

Número de pieza

componentes Descripción

Fabricante

A6259KA Datasheet PDF : 10 Pages

| |||

6259

8-BIT ADDRESSABLE

DMOS POWER DRIVER

FUNCTIONAL DESCRIPTION and INPUT REQUIREMENTS

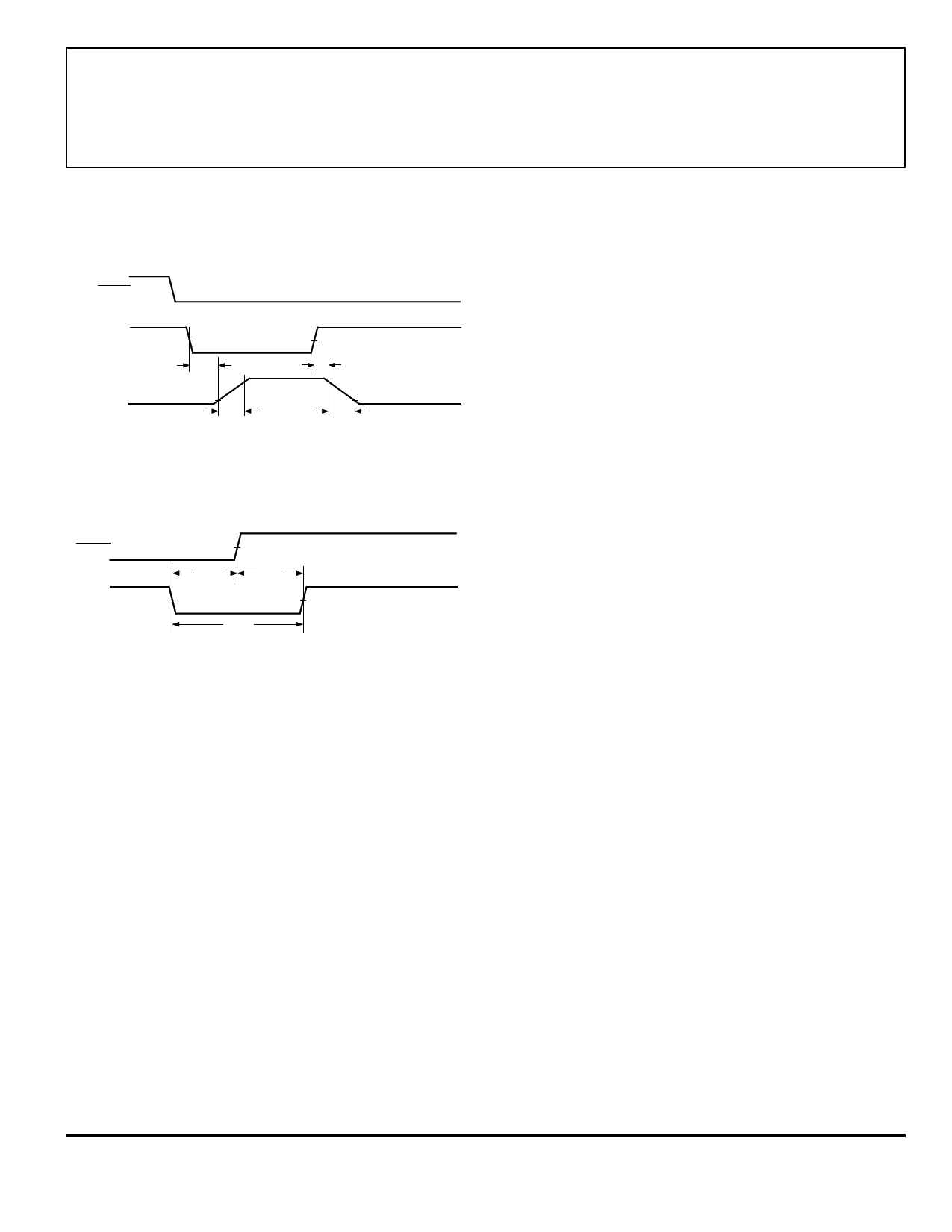

ENABLE

DATA

ADDRESSED

OUTPUT

50%

t PLH

10%

tr

t PHL

90%

tf

OUTPUT SWITCHING TIME

Dwg. WP-036

ENABLE

DATA

50%

t su(D)

t h(D)

50%

t w(D)

Dwg. WP-037

DATA INPUT REQUIREMENTS

Data Active Time Before Enable

(Data Set-Up Time), tsu(D) .............................................. 20 ns

Data Active Time After Enable

(Data Hold Time), th(D) ................................................... 20 ns

Data Pulse Width, tw(D) ....................................................... 40 ns

Input Logic High, VIH ................................................ ≥ 0.85VDD

Input Logic Low, VIL ................................................. ≤ 0.15VDD

Four modes of operation are selectable by controlling

the CLEAR and ENABLE inputs as shown above.

In the addressable-latch mode, data at the DATA input

is written into the addressed transparent latch. The

addressed output inverts the data input with all other

outputs remaining in their previous states.

In the memory mode, all outputs remain in their

previous states and are unaffected by the DATA or

address (Sn) inputs. To prevent entering erroneus data in

the latches, ENABLE should be held HIGH while the

address lines are changing.

In the demultiplexing/decoding mode, the addressed

output inverts the data input and all other outputs are OFF.

In the clear mode, all outputs are OFF and are unaf-

fected by the DATA or address (SN) inputs.

Given the appropriate inputs, when DATA is LOW

for a given address, the output is OFF; when DATA is

HIGH, the output is ON and can sink current.

www.allegromicro.com