MX429A Ver la hoja de datos (PDF) - MX-COM Inc

Número de pieza

componentes Descripción

Fabricante

MX429A Datasheet PDF : 20 Pages

| |||

1200/2400bps MSK Modem for Trunked Radio Systems

8

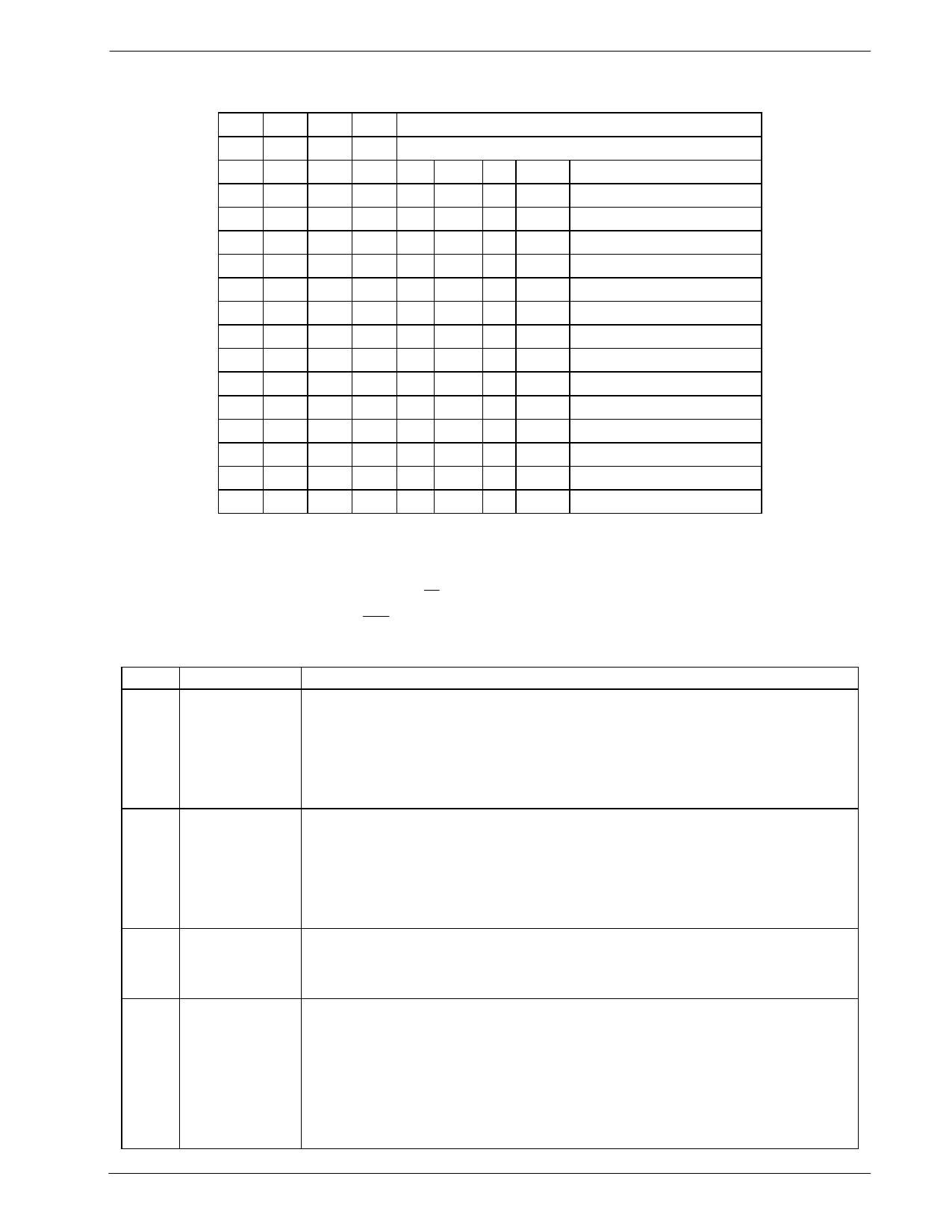

Table 4: Control Register

D7 D6 D5 D4 Reset counter and disable timer interrupts

0 0 0 0 Count and interrupt every

0 0 0 1“ “ “ 8

bits

0 0 1 0 " " " 16

bits

0 0 1 1 " " " 24

bits

0 1 0 0 " " " 32

bits

0 1 0 1 " " " 40

bits

0 1 1 0 " " " 48

bits

0 1 1 1 " " " 56

bits

1 0 0 0 " " " 64

bits

1 0 0 1 " " " 72

bits

1 0 1 0 " " " 80

bits

1 0 1 1 " " " 88

bits

1 1 0 0 " " " 96

bits

1 1 0 1 " " " 104

bits

1 1 1 0 " " " 112

bits

1 1 1 1 " " " 120

bits

Table 5: Timer Control Bits

MX429A

4.1.5 Status Register (A1 = 1, A0 = 1, R/ W = 1, Read Only)

When an interrupt is generated, the IRQ Output goes low with the Status Register bits indicating the sources

of the interrupt.

Bit

Description Function

Bit 0

Rx Data

D0: when set, causes an interrupt indicating that received data is ready to be read

D0

Ready

from the Rx Data Buffer. This data must be read within 8 bit periods.

Set when a byte of data is loaded into the Rx Data Buffer, if a frame (SYNC/SYNT)

word has been received.

Bit and Interrupt Cleared:

(i). by a read of the Status Register followed by a read of the Rx Data Buffer

(ii). by Rx Enable going Low.

Bit 1 Rx Checksum D1: when set, indicates that the error checking on the previous 6 bytes agreed with the

D1

True

received checksum. This function, which is valid when the Rx Data Ready bit (D0) is

set for the second byte of the received checksum, does not cause an interrupt.

Set: by a correct comparison between the received and generated checksums.

Cleared:

(i). by a read of the Status Register followed by a read of the Rx Data Buffer

(ii). by Rx Enable going Low.

Bit 2

Rx Carrier

D2: is a “Real Time” indication from the modem receiver's carrier detect circuit and

D2

Detect

does not cause an interrupt. When MSK tones are present at the receiver input this bit

goes High, for no MSK input this bit goes Low. When the Rx Enable bit (D2– Control

Register) is Low Rx Carrier Detect will go Low.

Bit 3

Tx Data

D3: when set, causes an interrupt to indicate that a byte of data should be written to

D3

Ready

the Tx Data Buffer within 8 bit periods.

Set:

(i). when the contents of the Tx Data Buffer are transferred to the Tx Data Register

(ii). when the Tx Enable is set (No interrupt is generated in this case.

Bit Cleared:

(i). by a read of the Status Register followed by a write to the Tx Data Buffer

(ii). by Tx Enable going Low.

Interrupt Cleared:

© 1998 MX-COM Inc.

www.mxcom.com Tel: 800 638-5577 336 744-5050 Fax: 336 744-5054

Doc. # 20480128.007

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

All trademarks and service marks are held by their respective companies.