87C196LA Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

87C196LA Datasheet PDF : 21 Pages

| |||

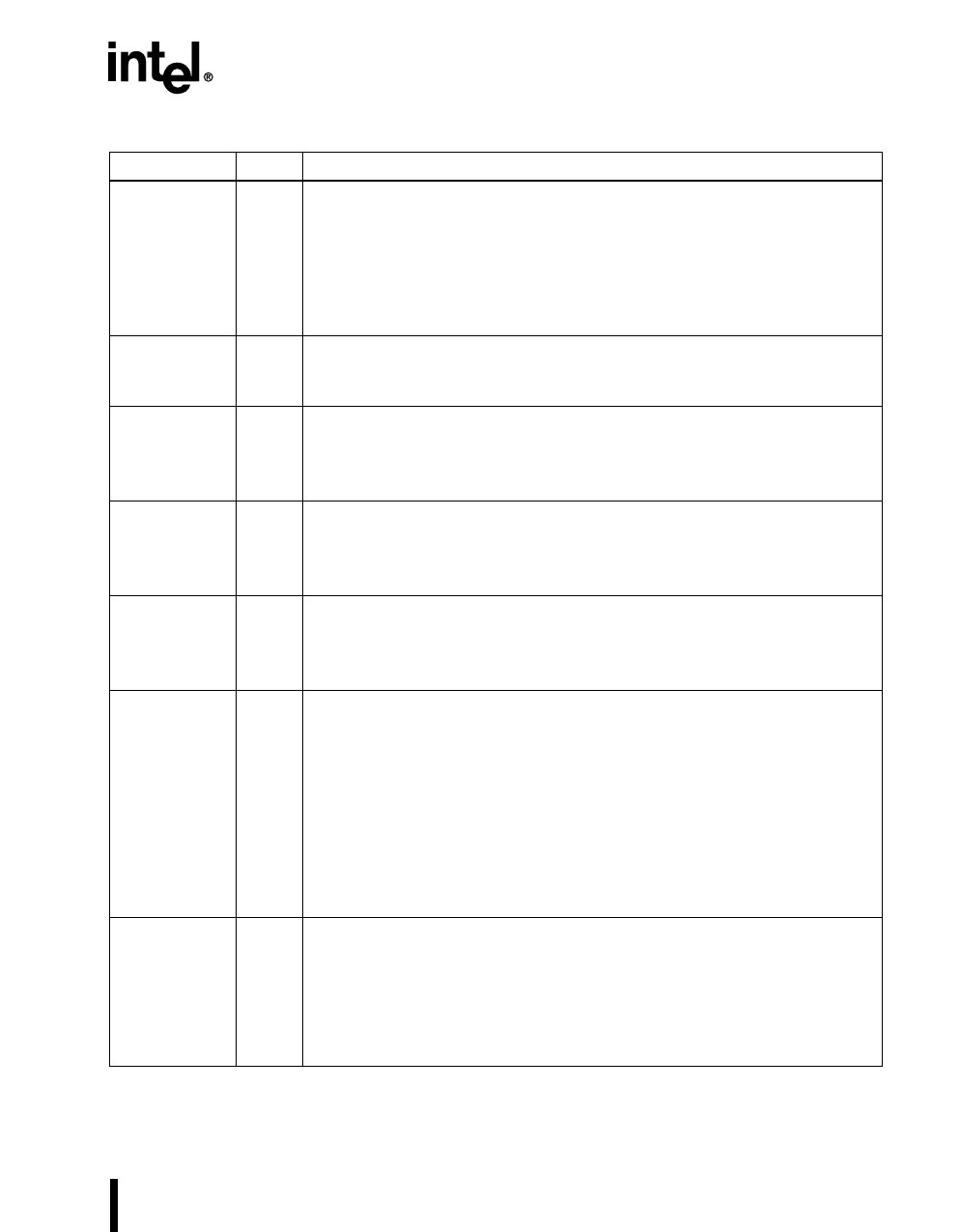

Name

ALE

ANGND

CLKOUT

COMP1:0

CPVER

EA#

EPA9:8

EPA3:0

AUTOMOTIVE — 87C196LA

Type

O

GND

O

O

O

I

I/O

Table 4. Signal Descriptions (Continued)

Description

Address Latch Enable

This active-high output signal is asserted only during external memory cycles.

ALE signals the start of an external bus cycle and indicates that valid address

information is available on the system address/data bus.

An external latch can use this signal to demultiplex the address from the

address/data bus.

ALE shares a package pin with P5.0 and ADV#.

Analog Ground

ANGND must be connected for A/D converter and port 0 operation. ANGND

and VSS should be nominally at the same potential.

Output

Output of the internal clock generator. You can select one of three frequencies:

f, f/2, or f/4. CLKOUT has a 50% duty cycle.

CLKOUT shares a package pin with P2.7 and PACT#.

Event Processor Array (EPA) Compare Pins

These signals are the outputs of the EPA compare-only channels.

COMP1:0 share package pins with the following signals: COMP0/P6.0/EPA8

and COMP1/P6.1/EPA9.

Cumulative Program Verification

During slave or programming, a high signal indicates that, while a low signal

indicates that an error occurred during the program operation.

CPVER shares a package pin with P2.6 and ONCE#.

External Access

This input determines whether memory accesses to special-purpose and

program memory partitions are directed to internal or external memory. These

accesses are directed to internal memory if EA# is held high and to

externalmemory if EA# is held low. For an access to any other memory location,

the value of EA# is irrelevant.

EA# also controls entry into the programming modes. If EA# is at VPP voltage

(typically +12.5 V) on the rising edge of RESET#, the microcontroller enters a

programming mode.

EA# is sampled and latched only on the rising edge of RESET#. Changing the

level of EA# after reset has no effect.

Event Processor Array (EPA) Capture/Compare Channels

High-speed input/output signals for the EPA capture/compare channels.

The EPA signals share package pins with the following signals:

EPA0/P1.0/T2CLK, EPA1/P1.1, EPA2/P1.2/T2DIR, EPA3/P1.3,

EPA8/P6.0/COMP0, and EPA9/P6.1/COMP1. EPA7:6 do not connect to

package pins. They cannot be used to capture an event, but they can function

as software timers. EPA5:4 are not implemented.

PRODUCT PREVIEW

9