CXD2497R Ver la hoja de datos (PDF) - Sony Semiconductor

Número de pieza

componentes Descripción

Fabricante

CXD2497R Datasheet PDF : 35 Pages

| |||

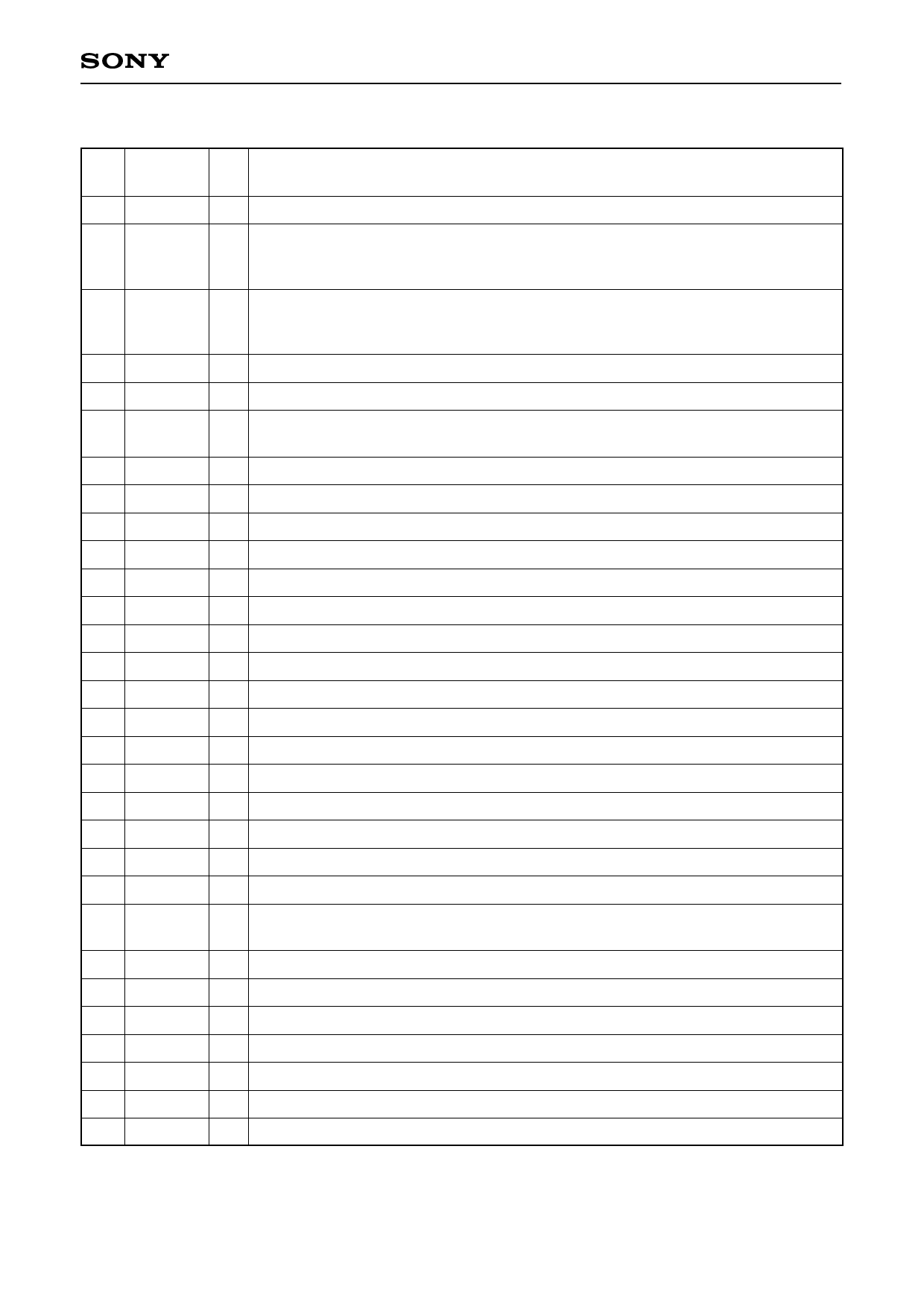

CXD2497R

Pin Description

Pin

No.

Symbol

1 VSS1

2 RST

3 SNCSL

4 ID

5 WEN

6 SSGSL

7 VDD1

8 VDD2

9 RG

10 VSS2

11 VSS3

12 H1

13 H2

14 VDD3

15 VDD4

16 XSHP

17 XSHD

18 XRS

19 PBLK

20 CLPDM

21 VSS4

22 OBCLP

23 ADCLK

24 VSS5

25 CKO

26 CKI

27 OSCO

28 OSCI

29 VDD5

30 MCKO

I/O

Description

— GND

Internal system reset input. High: Normal operation, Low: Reset control

I Normally apply reset during power-on.

Schmitt trigger input/No protective diode on power supply side

Control input used to switch sync system.

I

High: CKI sync, Low: MCKO sync

With pull-down resistor

O Vertical direction line identification pulse output.

O Memory write timing pulse output.

I Internal SSG enable.

High: Internal SSG valid, Low: External sync valid

With pull-down resistor

— 3.3V power supply. (Power supply for common logic block)

— 3.3V power supply. (Power supply for RG)

O CCD reset gate pulse output.

— GND

— GND

O CCD horizontal register clock output.

O CCD horizontal register clock output.

— 3.3 to 5.0V power supply. (Power supply for H1/H2)

— 3.3V power supply. (Power supply for CDS block)

O CCD precharge level sample-and-hold pulse output.

O CCD data level sample-and-hold pulse output.

O Sample-and-hold pulse output for analog/digital conversion phase alignment.

O Pulse output for horizontal and vertical blanking period pulse cleaning.

O CCD dummy signal clamp pulse output.

— GND

O CCD optical black signal clamp pulse output.

O

Clock output for analog/digital conversion IC.

Logical phase adjustment possible using the serial interface data.

— GND

O Inverter output.

I Inverter input.

O Inverter output for oscillation. When not used, leave open or connect a capacitor.

I Inverter input for oscillation.

When not used, fix low.

— 3.3V power supply. (Power supply for common logic block)

O System clock output for signal processing IC.

–3–