CAT1163 Ver la hoja de datos (PDF) - Catalyst Semiconductor => Onsemi

Número de pieza

componentes Descripción

Fabricante

CAT1163

CAT1163 Datasheet PDF : 12 Pages

| |||

CAT1163

ACKNOWLEDGE

After a successful data transfer, each receiving device

is required to generate an acknowledge. The

acknowledging device pulls down the SDA line during

the ninth clock cycle, signaling that it received the 8 bits

of data.

The CAT1163 responds with an acknowledge after

receiving a START condition and its slave address. If the

device has been selected along with a write operation,

it responds with an acknowledge after receiving each 8-

bit byte.

When the CAT1163 begins a READ mode it transmits 8

bits of data, releases the SDA line and monitors the line

for an acknowledge. Once it receives this acknowledge,

the CAT1163 will continue to transmit data. If no

acknowledge is sent by the Master, the device terminates

data transmission and waits for a STOP condition.

WRITE OPERATIONS

Byte Write

In the Byte Write mode, the Master device sends the

START condition and the slave address information

(with the R/W bit set to zero) to the Slave device. After

the Slave generates an acknowledge, the Master sends

a 8-bit address that is to be written into the address

pointers of the CAT1163. After receiving another

acknowledge from the Slave, the Master device transmits

the data to be written into the addressed memory location.

The CAT1163 acknowledges once more and the Master

generates the STOP condition. At this time, the device

begins an internal programming cycle to non-volatile

memory. While the cycle is in progress, the device will not

respond to any request from the Master device.

Page Write

The CAT1163 writes up to 16 bytes of data in a single

write cycle, using the Page Write operation. The page

write operation is initiated in the same manner as the byte

write operation, however instead of terminating after the

initial byte is transmitted, the Master is allowed to send up

to 15 additional bytes. After each byte has been

transmitted, the CAT1163 will respond with an

acknowledge and internally increment the lower order

address bits by one. The high order bits remain unchanged.

If the Master transmits more than 16 bytes before sending

the STOP condition, the address counter ‘wraps around,’

and previously transmitted data will be overwritten.

When all 16 bytes are received, and the STOP condition

has been sent by the Master, the internal programming

cycle begins. At this point, all received data is written to

the CAT1163 in a single write cycle.

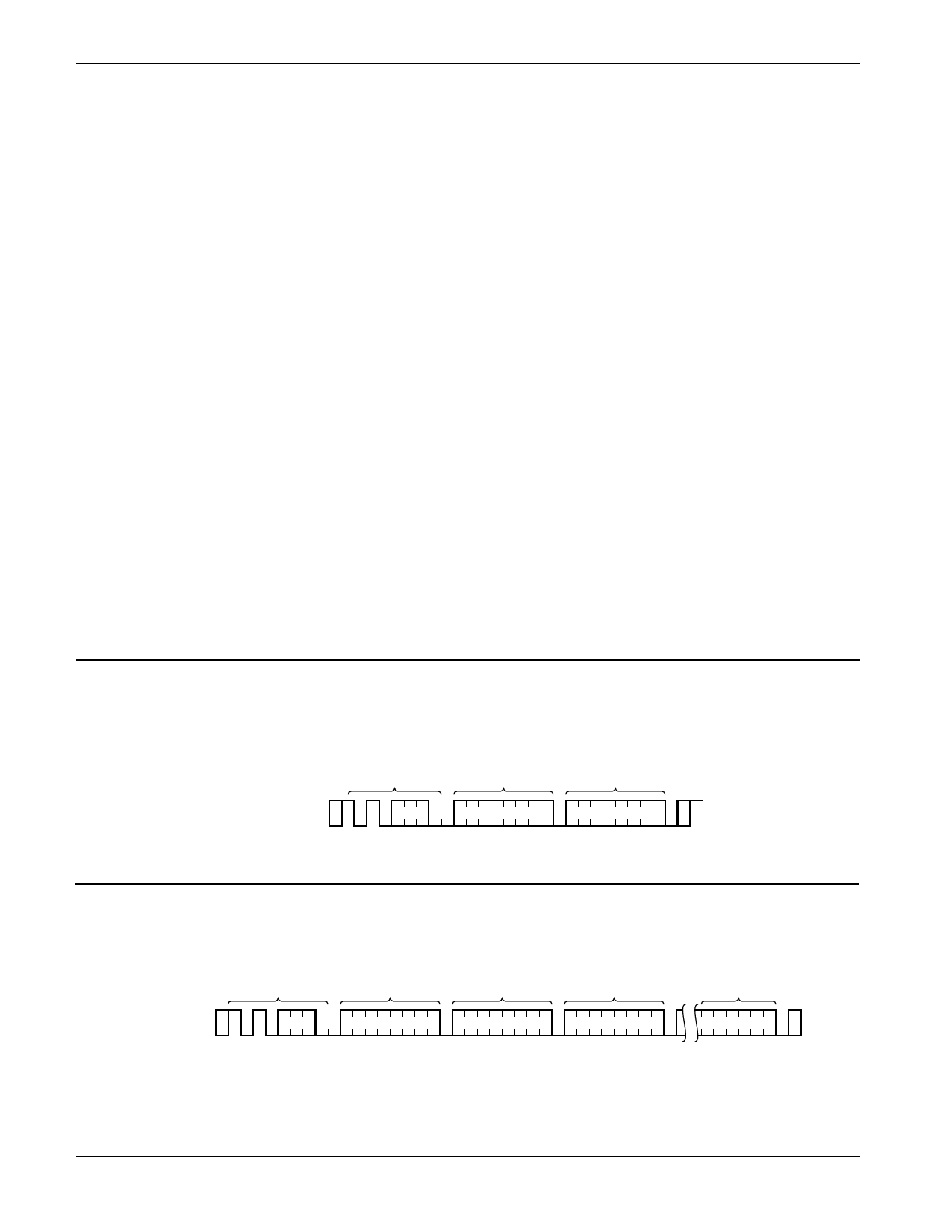

Figure 7. Byte Write Timing

S

T

BUS ACTIVITY: A

MASTER R

T

SLAVE

ADDRESS

BYTE

ADDRESS

S

T

DATA

O

P

SDA LINE S

P

A

A

A

C

C

C

K

K

K

Figure 8. Page Write Timing

S

T

BUS ACTIVITY: A

MASTER R

T

SDA LINE S

SLAVE

ADDRESS

BYTE

ADDRESS (n)

A

A

C

C

K

K

DATA n

DATA n+1

A

A

C

C

K

K

S

T

DATA n+15 O

P

P

A

C

K

Doc. No. 3003, Rev. C

8