ACT8942 Ver la hoja de datos (PDF) - Active-Semi, Inc

Número de pieza

componentes Descripción

Fabricante

ACT8942 Datasheet PDF : 44 Pages

| |||

ACT8942

Rev 2, 15-Nov-12

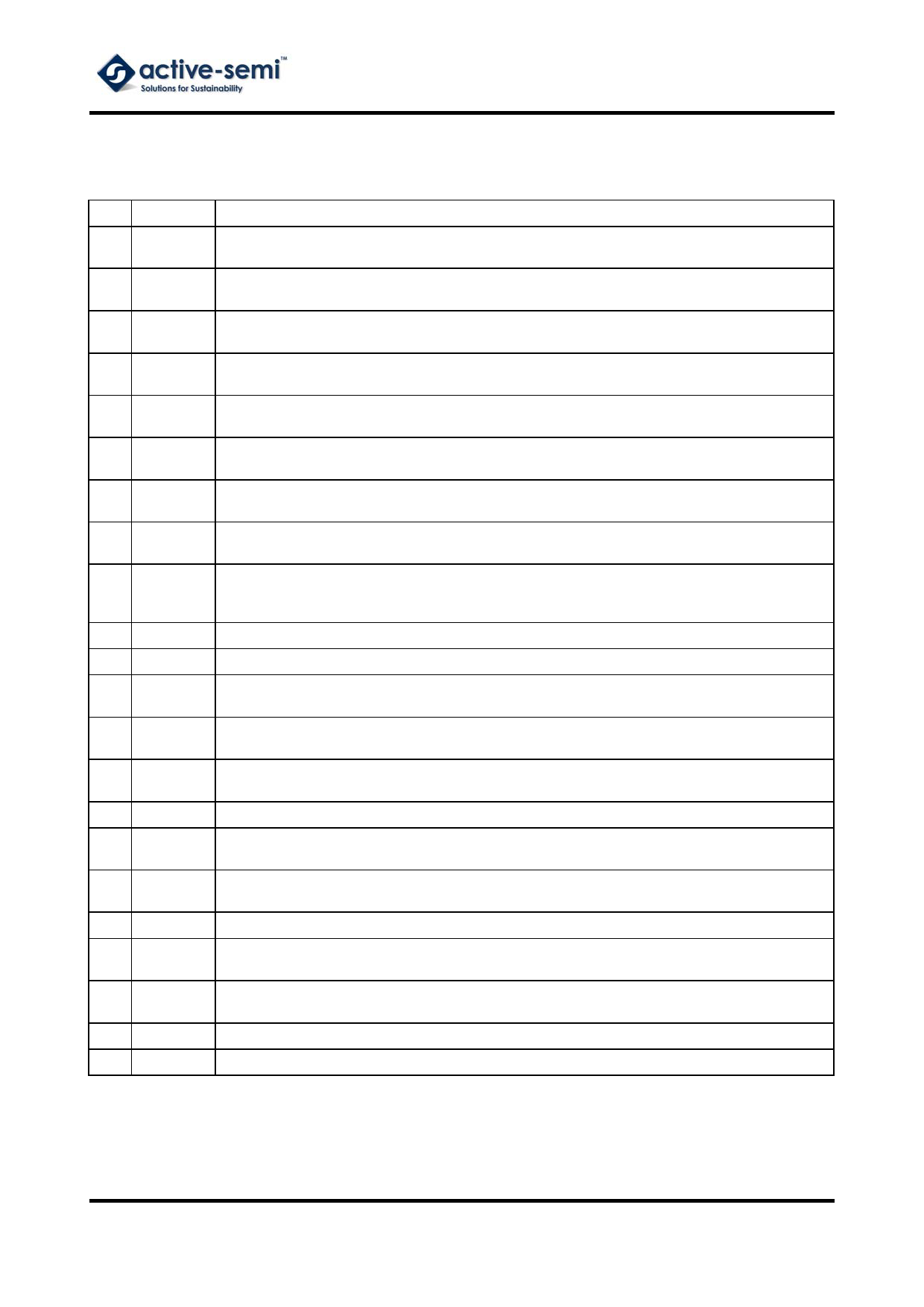

PIN DESCRIPTIONS

PIN NAME

DESCRIPTION

1

REFBP

Reference Bypass. Connect a 0.047μF ceramic capacitor from REFBP to GA. This pin is

discharged to GA in shutdown.

2

OUT1 Output Feedback Sense for REG1.

3

GA

Analog Ground. Connect GA directly to a quiet ground node. Connect GA, GP12 and GP3

together at a single point as close to the IC as possible.

4

OUT4

REG4 output. Capable of delivering up to 80mA of output current. Connect a 1.5µF ceramic

capacitor from OUT4 to GA. The output is discharged to GA with 1.5kΩ resistor when disabled.

5

OUT5

REG5 output. Capable of delivering up to 320mA of output current. Connect a 3.3µF ceramic

capacitor from OUT5 to GA. The output is discharged to GA with 1.5kΩ resistor when disabled.

6

INL

Power Input for REG4, REG5, REG6, and REG7. Bypass to GA with a high quality ceramic

capacitor placed as close to the IC as possible.

7

OUT7

REG7 output. Capable of delivering up to 320mA of output current. Connect a 3.3µF ceramic

capacitor from OUT7 to GA. The output is discharged to GA with 1.5kΩ resistor when disabled.

8

OUT6

REG6 output. Capable of delivering up to 320mA of output current. Connect a 3.3µF ceramic

capacitor from OUT6 to GA. The output is discharged to GA with 1.5kΩ resistor when disabled.

Master Enable Input. Drive nPBIN to GA through a 50kΩ resistor to enable the IC, drive nPBIN

9

nPBIN directly to GA to assert a manual reset condition. Refer to the nPBIN Multi-Function Input section

for more information. nPBIN is internally pulled up to VSYS through a 35kΩ resistor.

10 PWRHLD Power Hold Input. Refer to the Control Sequences section for more information.

11 nRSTO Active Low Reset Output. See the nRSTO Output section for more information.

12

nIRQ

Open-Drain Interrupt Output. nIRQ is asserted any time an unmasked fault condition exists or a

charger interrupt occurs. See the nIRQ Output section for more information.

13

nPBSTAT

Active-Low Open-Drain Push-Button Status Output. nPBSTAT is asserted low whenever the

nPBIN is pushed, and is high-Z otherwise. See the nPBSTAT Output section for more information.

14

GP3

Power Ground for REG3. Connect GA, GP12, and GP3 together at a single point as close to the

IC as possible.

15

SW3 Switching Node Output for REG3.

16

VP3

Power Input for REG3. Bypass to GP3 with a high quality ceramic capacitor placed as close to the

IC as possible.

17

OUT3 Output Feedback Sense for REG3.

18 PWREN Power Enable Input. Refer to the Control Sequences section for more information.

19

nLBO

Low Battery Indicator Output. nLBO is asserted low whenever the voltage at LBI is lower than

1.2V, and is high-Z otherwise. See the Precision Voltage Detector section for more information.

20

LBI

Low Battery Input. The input voltage is compared to 1.2V and the output of this comparison drives

nLBO. See the Precision Voltage Detector section for more information.

21

ACIN AC Input Supply Detection. See the Charge Current Programming section for more information.

22 CHGLEV Charge Current Selection Input. See the Charge Current Programming section for more information.

Innovative PowerTM

-5-

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMUTM and ActivePathTM are trademarks of Active-Semi.

I2CTM is a trademark of NXP.

www.active-semi.com

Copyright © 2012 Active-Semi, Inc.