LT1064 Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Fabricante

LT1064 Datasheet PDF : 16 Pages

| |||

LTC1064

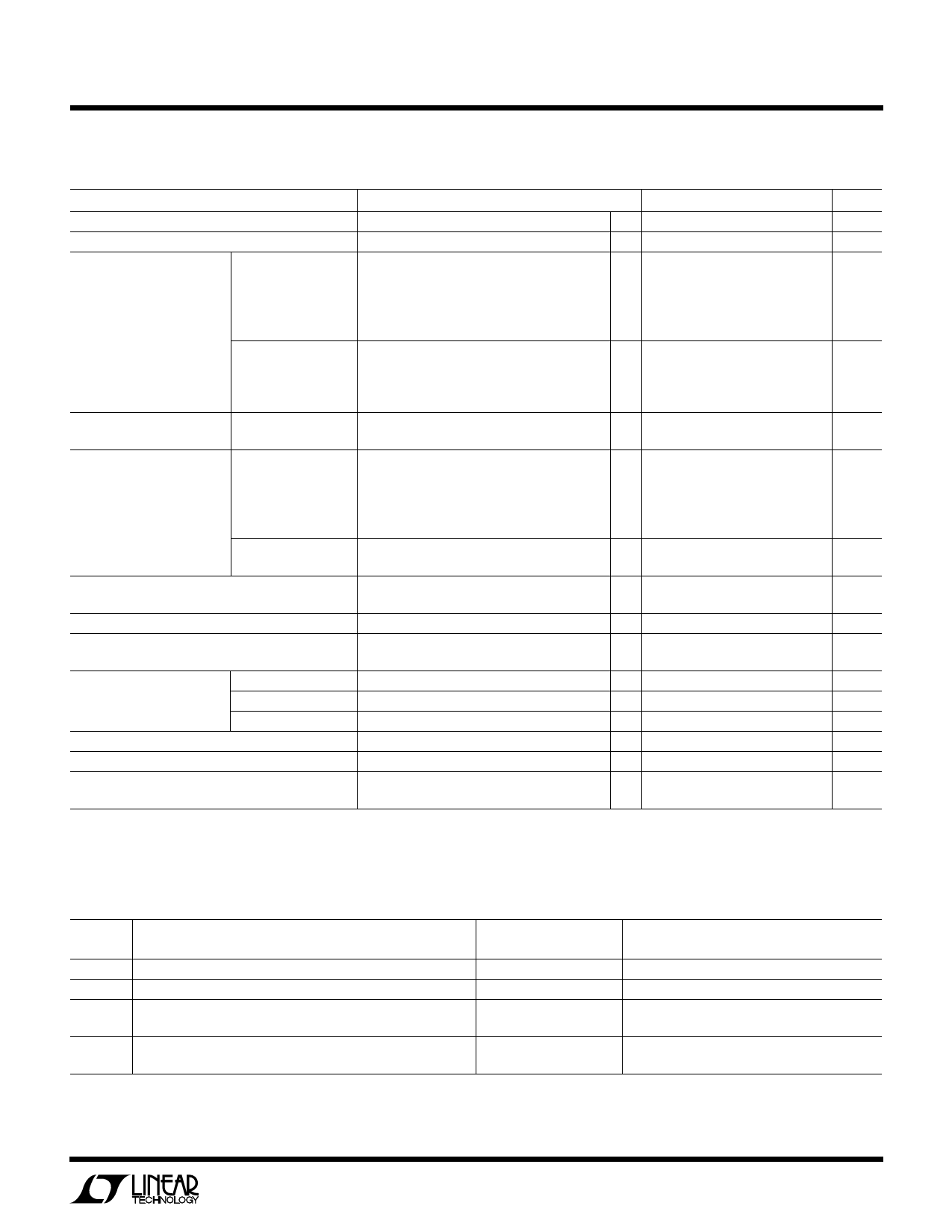

ELECTRICAL CHARACTERISTICS

(Complete Filter) VS = ±5V, TA = 25°C, TTL clock input level, unless otherwise specified.

PARAMETER

Center Frequency Range, fO

Input Frequency Range

Clock-to-Center Frequency

Ratio, fCLK/fO

LTC1064

LTC1064A (Note 1)

LTC1064

LTC1064A (Note 1)

Clock-to-Center Frequency

Ratio, Side-to-Side Matching

Clock-to-Center Frequency

Ratio, fCLK/fO (Note 2)

LTC1064

LTC1064A (Note 1)

LTC1064

LTC1064A (Note 1)

Q Accuracy

LTC1064

LTC1064 A (Note 1)

fO Temperature Coefficient

Q Temperature Coefficient

DC Offset Voltage

Clock Feedthrough

Maximum Clock Frequency

Power Supply Current

VOS1 (Table 1)

VOS2 (Table 1)

VOS3 (Table 1)

CONDITIONS

VS = ±8V, Q ≤ 3

fCLK = 1MHz, fO = 20kHz, Pin 17 High

Sides A, B, C: Mode 1,

R1 = R3 = 5k, R2 = 5k, Q = 10,

Sides D: Mode 3, R1 = R3 = 50k

R2 = R4 = 5k

Same as Above, Pin 17 Low, fCLK = 1MHz

fO = 10kHz

Sides A, B, C

Side D

fCLK = 1MHz

fCLK = 4MHz, fO = 80kHz, Pin 17 High

Sides A, B, C: Mode 1, VS = ±7.5V

R1 = R3 = 50k, R2 = 5k, Q = 5

Side D: Mode 3, R1 = R3 = 50k

R2 = R4 = 5k, fCLK = 4MHz

Same as Above, Pin 17 Low

fCLK = 4MHz, fO = 40kHz

Sides A, B, C: Mode 1, Q = 10

Side D: Mode 3, fCLK = 1MHz

Mode 1, 50:1, fCLK < 2MHz

Mode 1, 100:1, fCLK < 2MHz

Mode 3, fCLK < 2MHz

fCLK = 1MHz, 50:1 or 100:1

fCLK = 1MHz, 50:1 or 100:1

fCLK = 1MHz, 50:1 or 100:1

fCLK < 1MHz

Mode 1, Q < 5, VS ≥ ±5V

MIN

TYP

MAX

UNITS

0.1 to 140

kHz

0 to 1

MHz

50 ± 0.3

%

q

50 ± 0.8

%

q

50 ± 0.9

%

100 ± 0.3

%

q

100 ± 0.8

%

q

100 ± 0.9

0.4

%

q

1

%

50 ± 0.6

%

50 ± 1.3

%

100 ± 0.6

%

100 ± 1.3

%

q

±2

6

%

q

±3

8

%

±1

ppm/°C

±5

ppm/°C

±5

ppm/°C

q

2

15

mV

q

3

45

mV

q

3

45

mV

0.2

mVRMS

7

MHz

9

12

23

mA

q

26

mA

The q denotes specifications which apply over the full operating

temperature range.

Note 1: Contact LTC Marketing.

Note 2: Not tested, guaranteed by Design.

Table 1. Output DC Offsets, One 2nd Order Section

MODE

1

1b

2

3

VOSN

PINS 2, 11, 14, 23

VOS1 [(1/Q) + 1 + HOLP] – VOS3/Q

VOS1 [(1/Q) + 1 + (R2/R1)] – VOS3/Q

VOS1 [(1 + (R2/R1) + (R2/R3) + (R2/R4) – VOS3(R2/R3)]

× [R4/(R2 + R4)] + VOS2[R2/(R2 + R4)]

VOS2

VOSBP

PINS 3, 10, 15, 22

VOS3

VOS3

VOS3

VOS3

VOSLP

PINS 4, 9, 16, 21

VOSN – VOS2

~(VOSN – VOS2)[1 + (R5/R6)]

VOSN – VOS2

VOS1[1 + (R4/R1) + (R4/R2) + (R4/R3)]

– VOS2(R4/R2) – VOS3(R4/R3)

3