MP156 Ver la hoja de datos (PDF) - Monolithic Power Systems

Número de pieza

componentes Descripción

Fabricante

MP156

MP156 Datasheet PDF : 20 Pages

| |||

MP156 –SMALL, ENERGY-EFFICIENT, OFF-LINE REGULATOR

Over-Load Protection (OLP)

The peak current and the switching frequency

both increase as the load increases. When the

switching frequency and peak current reach their

maximums, the output voltage decreases if the

load continues to increase so that the FB voltage

drops below the OLP point.

The MP156 continuously monitors FB. When the

FB voltage drops below 1.7V—which is

considered as an error flag—the timer starts.

Removing the error flag resets the timer. If the

timer reaches 170ms (fs=37kHz), OLP occurs.

This timer duration avoids triggering OLP when

the power supply starts up or is in a load

transition phase: The power supply should start

up in less than 170ms (fs=37kHz). Changing the

switching frequency changes the OLP delay time

as per the following equation:

τDelay

≈ 170ms ×

37kHz

fs

Short-Circuit Protection (SCP)

The MP156 monitors the peak current, and shuts

down when the peak current rises above 450mA

through short-circuit protection. The power

supply resumes operation with the removal of the

fault.

Thermal Shutdown (TSD)

To prevent any lethal thermal damage, the

MP156 shuts down switching when the inner

temperature exceeds 150°C. During the thermal

shutdown (TSD), the VCC capacitor discharges

to 2.4V, and then the internal high voltage

regulator re-charges by.

Open-Loop Detection

If VFB is less than 60mV, the IC will stop switching

and a re-start cycle will begin. During start-up,

the open loop detection is blanked for 128

switching cycles.

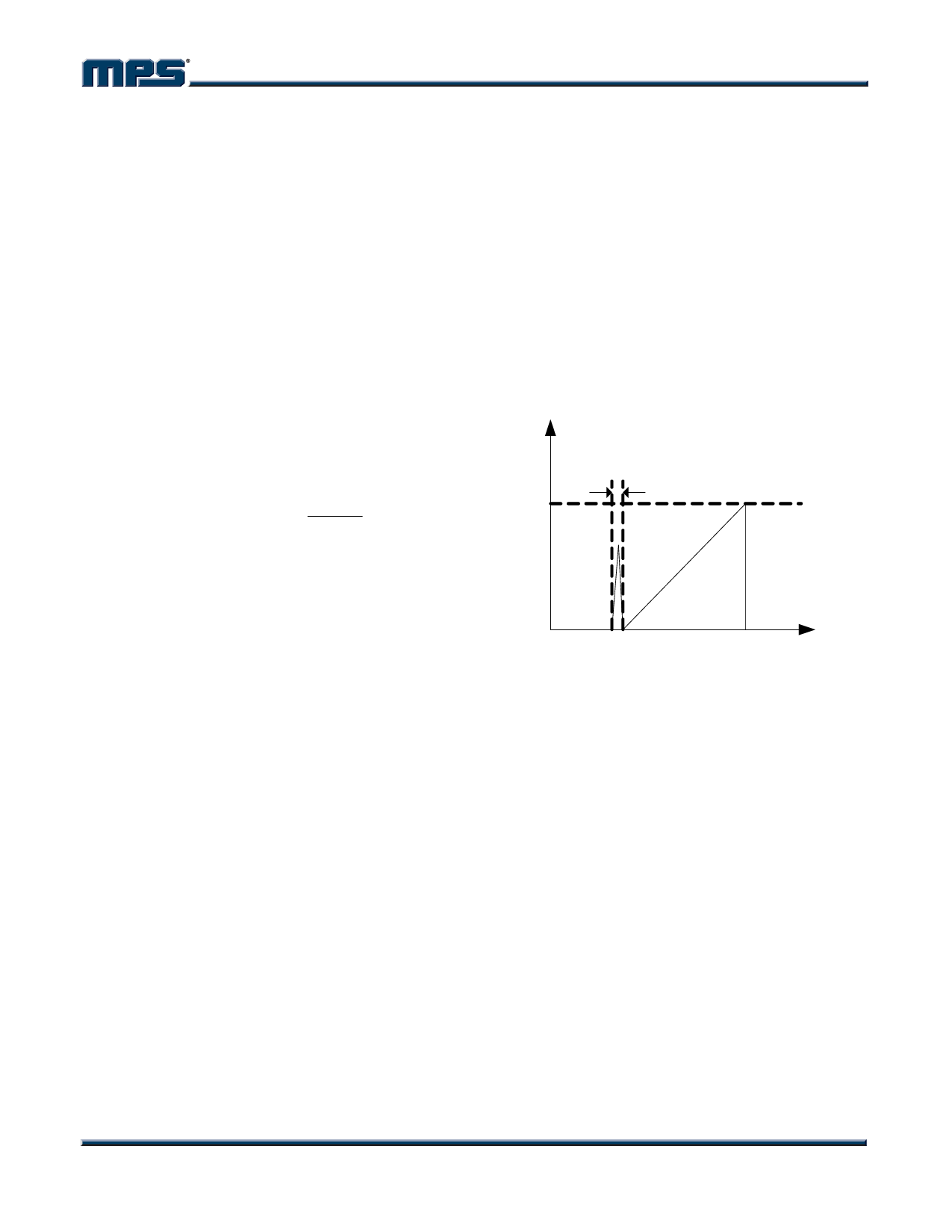

Leading-Edge Blanking

An internal leading-edge blanking (LEB) unit—

between the current sense resistor inside the IC

and the current comparator input—avoids

premature switching pulse termination due to

parasitic capacitance,. During the blanking time,

the current comparator is disabled and can not

turn off the external MOSFET. Figure 6 shows

the leading-edge blanking.

VLimit

TLEB=350nS

t

Figure 6: Leading-Edge Blanking

MP156 Rev. 1.15

www.MonolithicPower.com

11

4/21/2016

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2016 MPS. All Rights Reserved.