DNC3X3625 Ver la hoja de datos (PDF) - Agere -> LSI Corporation

Número de pieza

componentes Descripción

Fabricante

DNC3X3625 Datasheet PDF : 32 Pages

| |||

DNC3X3625

10/100 Mbits/s Ethernet Transceiver Macrocell

Advance Data Sheet

March 2000

Signal Information (continued)

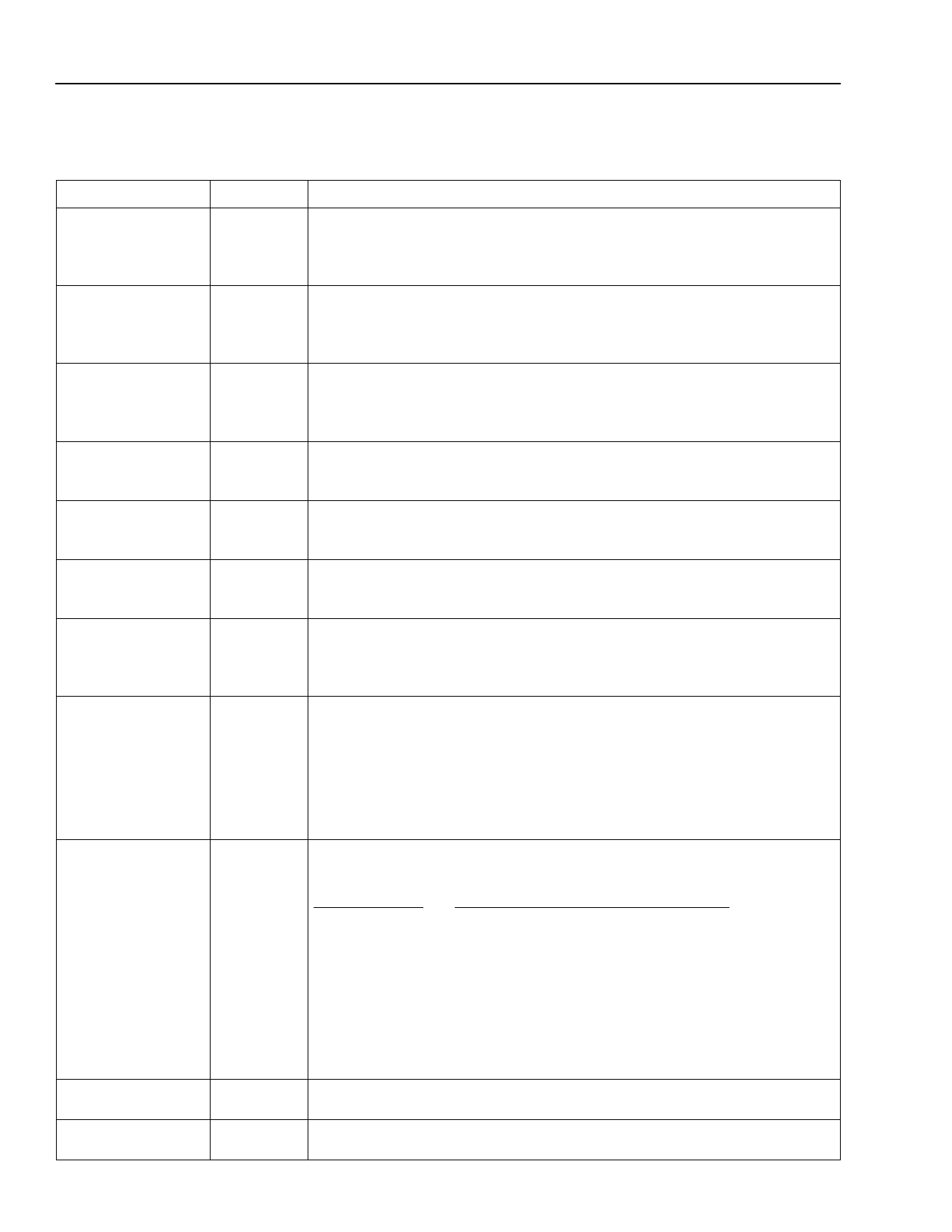

Table 6. Control/Status Signals

Signal

AUTO_EN[5:0]

F_DUP[5:0]

4

CRS_SEL[5:0]

SER_SEL_PIN[5:0]

CARIN_IN[5:0]

EDBT[5:0]

SDBT[5:0]

SPEED_PIN[5:0]

MGT_ADD[4:2]

Type

I

I

I

I

I

I

I

I

I

Description

Autonegotiation Enable. When this signal is high, autonegotiation is

enabled. Pulsing this signal will cause autonegotiation to restart. This input

has the same function as register 0, bit 12. This input and the register bit are

ANDed together.

Full-Duplex Mode. When this signal is set high, the PHY will be in full-

duplex mode. A low on this signal will put it in half-duplex mode. This signal

is ignored when autonegotiation is enabled. This is the same function as

register 0, bit 8. This input and the register bit are ORed together.

Carrier Sense Select. This signal may be used to select the mode of

MCRS operation. When this signal is pulled high, MCRS will be asserted on

receive activity only. This is the same function as register 29, bit 10. This

input and the register bit are ORed together.

Serial Mode Select. This signal may be used to set the SERIAL_SEL func-

tion of register 30, bit 1 by pulling it high, if station management is unavail-

able. This input and the register bit are ORed together.

Carrier Integrity Enable. If this signal is pulled high, it will enable the

carrier integrity function of register 29, bit 3, if station management is

unavailable. This input and the register bit are ORed together.

Encoder/Decoder Bypass. If this signal is pulled high, it will enable the

encoder/decoder bypass function of register 29, bit 6, if station management

is unavailable. This input and the register bit are ORed together.

Scrambler/Descrambler. This signal may be used to enable the scrambler/

descrambler bypass function by pulling this signal high, if station manage-

ment is unavailable. This is the same function as register 29, bit 4. This

input and the register bit are ORed together.

Speed. This signal can be used to select the operating speed and is the

same function as register 0, bit 13:

s If this signal is pulled high, it will enable 100 Mbits/s operation.

s If this signal is pulled low, it will enable 10 Mbits/s operation.

This signal is ignored when autonegotiation is enabled. This signal and the

register bit are ANDed.

Management Address [4:2]. These signals set the management

addresses and are decoded as follows:

MGT_ADD[4:2]

000

001

010

011

100

101

110

111

PHY 0, PHY 1, PHY 2, PHY 3, PHY 4, PHY 5

0, 1, 2, 3, 4, 5

8, 9, 10, 11, 12, 13

16, 17, 18, 19, 20, 21

24, 25, 26, 27, 28, 29

6, 7, 8, 9, 10, 11

12, 13, 14, 15, 16, 17

18, 19, 20, 21, 22, 23

0, 0, 0, 0, 0, 0, 0, 0

REV_ADD

FX_MODE[5:0]

10

I

Reverse Phy Address. Reverse the order of Ports for Management

Access. (PHY0 is highest address, PHY5 is lowest address)

I

FX_MODE. When this signal is high, it puts DNC3X3625 in fiber-optic

mode. This signal is ORed with register 29, bit 0 [29.0].