QL6325-E Ver la hoja de datos (PDF) - QuickLogic Corporation

Número de pieza

componentes Descripción

Fabricante

QL6325-E Datasheet PDF : 56 Pages

| |||

QL6325E Eclipse-E Data Sheet Rev. F

Instruction

S1

S2

S3

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Table 3: ECU Mode Select Criteria

Operation

ECU Performancea, -8 WCC

tPD

tSU

tCO

Multiply

6.6 ns max

Multiply-Add

Accumulateb

8.8 ns max

3.9 ns min

1.2 ns max

Add

Multiply (registered)c

3.1 ns max

9.6 ns min

1.2 ns max

Multiply- Add (registered)

9.6 ns min

1.2 ns max

Multiply - Accumulate

9.6 ns min

1.2 ns max

Add (registered)

3.9 ns min

1.2 ns max

a. tPD, tSU and tCO do not include routing paths in/out of the ECU block.

b. Internal feedback path in ECU restricts max clk frequency to 238 MHz.

c. B [15:0] set to zero.

NOTE: Timing numbers in Table 3 represent -8 Worst Case Commercial conditions.

Phase Locked Loop (PLL) Information

Instead of requiring extra components, designers simply need to instantiate one of the pre-configured models

(described in this section). The QuickLogic built-in PLLs support a wider range of frequencies than many other

PLLs. These PLLs also have the ability to support different ranges of frequency multiplications or divisions,

driving the device at a faster or slower rate than the incoming clock frequency. When PLLs are cascaded, the

clock signal must be routed off-chip through the PLLPAD_OUT pin prior to routing into another PLL; internal

routing cannot be used for cascading PLLs.

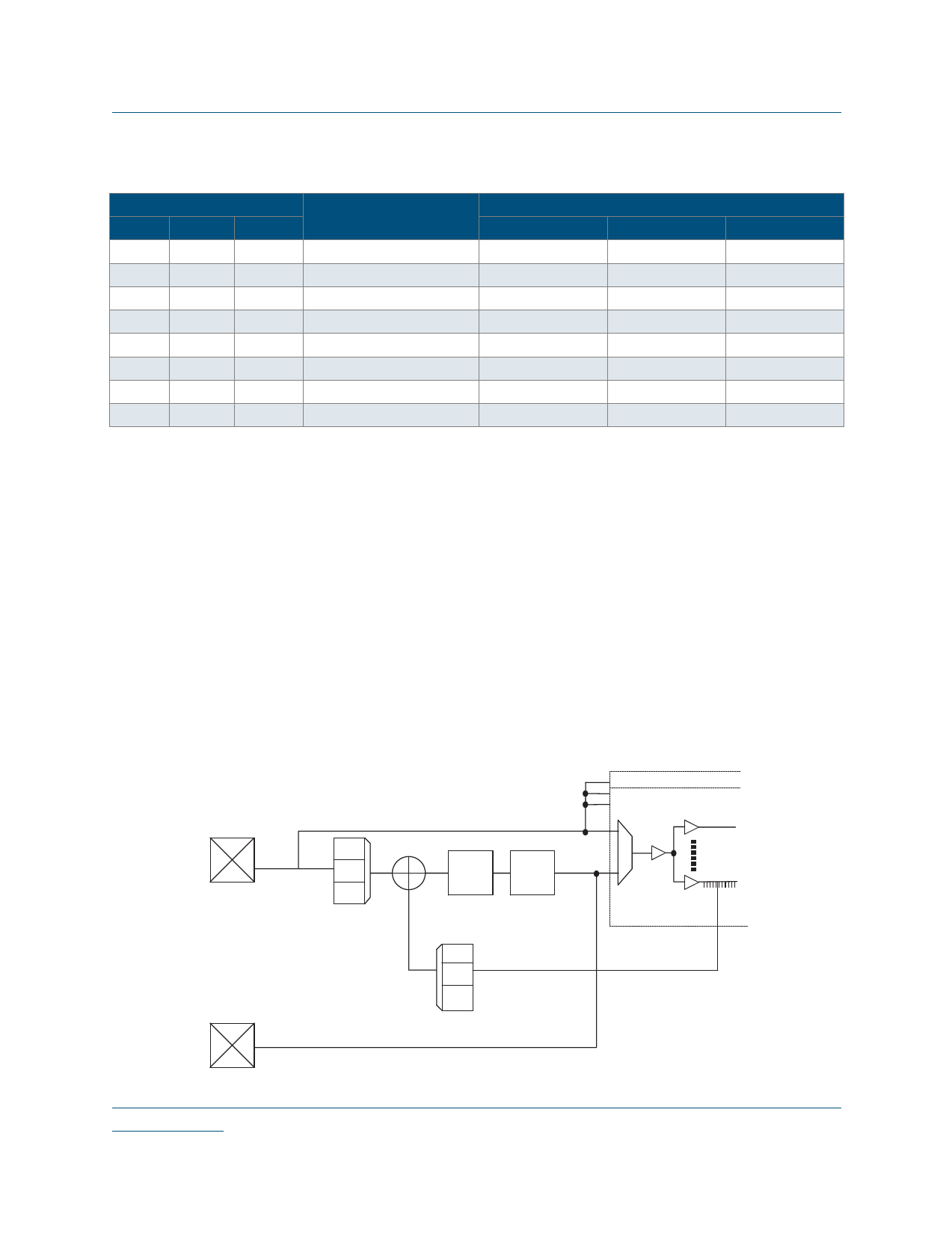

Figure 6 illustrates a QuickLogic PLL.

Figure 6: PLL Block Diagram

FIN

Frequency Divide

PLL Bypass

_..1

_.. 2

+

_.. 4

-

Filter

vco

1st Quadrant

2nd Quadrant

3rd Quadrant

4th Quadrant

Clock

Tree

FOUT

Frequency Multiply

_..1

_..2

_..4

6

•

•••

••

www.quicklogic.com

© 2005 QuickLogic Corporation