GL602USB Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Fabricante

GL602USB Datasheet PDF : 35 Pages

| |||

4. FUNCTIONAL DESCRIPTION

The Genesys Logic GL602USB micro-controller is optimized for PC keyboard. This USB microcontroller

conforms to the low-speed (1.5Mbps) requirements of the USB Specification version 1.1. The micro-controller is a

self-contained unit with an USB SIE, an USB transceiver, an 8-bit RISC-like microcontroller, a timer, data and

program memories. It supports one USB device address and four endpoints (include endpoint 0).

4.1 MEMORY ORGANIZATION

The memory in the microcontroller is organized into user program memory in program ROM and data memory

in SRAM space.

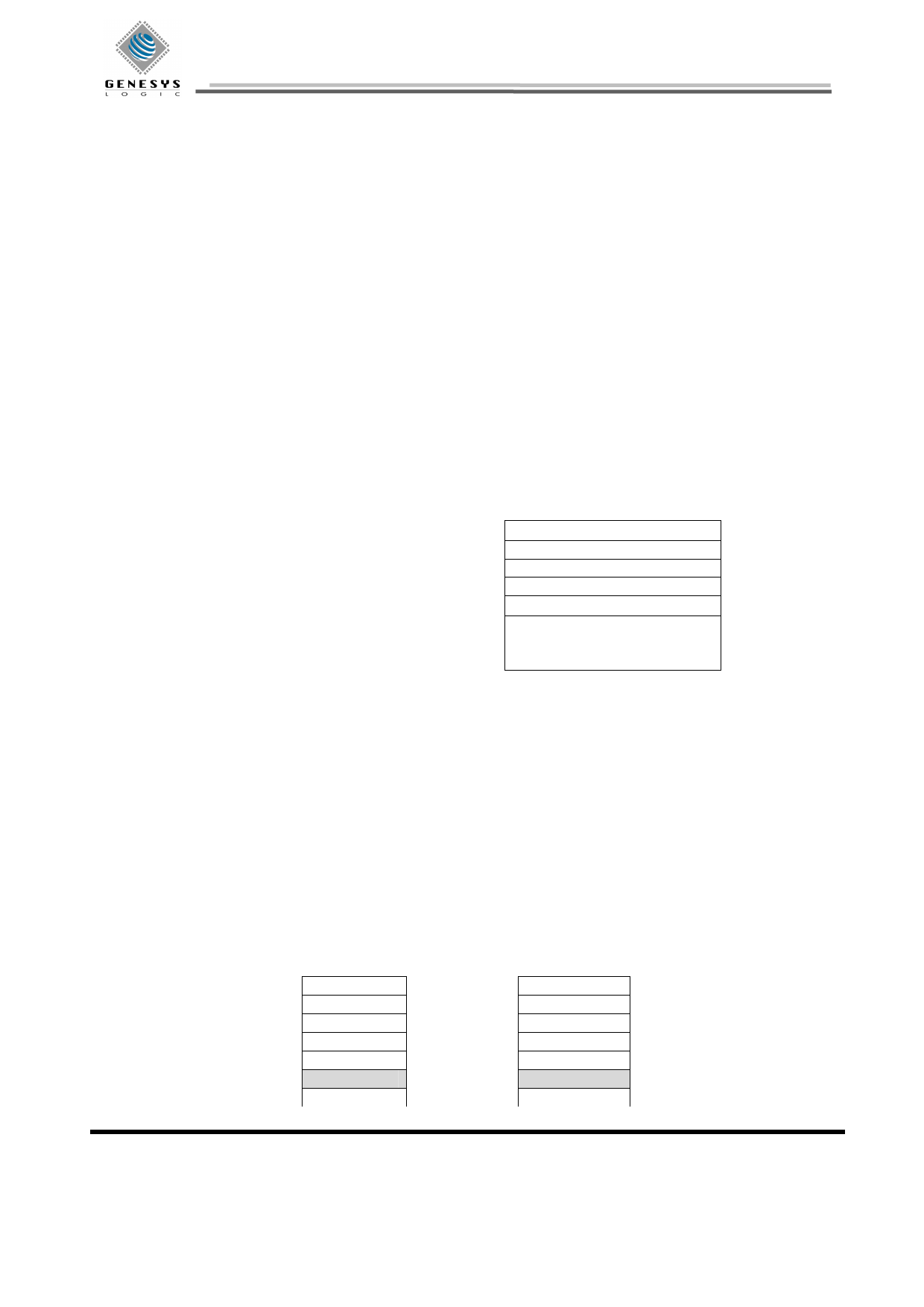

4.1.1 Program Memory Organization

The 12-bit Program Counter (PC) is capable of addressing 4K x 14 of program space. All of the 4K * 14 ROM

space can be used. The program memory space is divided into two functional groups: Interrupt Vectors and

program code. After a reset, the Program Counter points to location zero of the program space and all registers

are reset to the default value. After a timer interrupt, the Program Counter points the location 0x0004 of the

program space.

After Reset

Address

→ 0x0000 Reset Vector

After Timer Interrupt

→ 0x0004 Timer Interrupt Vector

0x0005

4K x 14 ROM

0x0FFF

Figure 4-1 Program Memory Space

4.1.2 Data Memory Organization

The data memory is partitioned into two Banks that contain the General Purpose Registers, MCU Function

Registers and USB Function Registers. Bit BS is the bank select bit.

BS (STATUS<5>) = 1 → Bank 1

BS (STATUS<5>) = 0 → Bank 0

The lower locations of each Bank are reserved for MCU Function Registers and USB Function Registers.

Above the MCU Function Registers and USB Function Registers are General Purpose Registers implemented

as SRAM. Both Bank 0 and Bank 1 contain MCU Function Registers. USB Function Registers are located in

Bank 0. Some “high use” MCU Function Registers from Bank 0 are mirrored in Bank 1 for code reduction and

quicker access.

Data

Memory

Address

00h

01h

02h

03h

04h

05h

06h

INDR

TIMER

PCL

STATUS

INDAR

PORT1

Data Memory

Address

80h

INDR

81h

PSCON

82h

PCL

83h

STATUS

84h

INDAR

85h

86h

PORT1CON

Revision 1.6

-9-

02/28/2000