ATT3042 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Fabricante

ATT3042 Datasheet PDF : 80 Pages

| |||

ATT3000 Series Field-Programmable Gate Arrays

Data Sheet

February 1997

Configuration Memory

The static memory cell used for the configuration mem-

ory in the FPGA has been designed specifically for

high reliability and noise immunity. Integrity of the

FPGA configuration memory based on this design is

ensured even under various adverse conditions. Com-

pared with other programming alternatives, static mem-

ory is believed to provide the best combination of high

density, high performance, high reliability, and compre-

hensive testability.

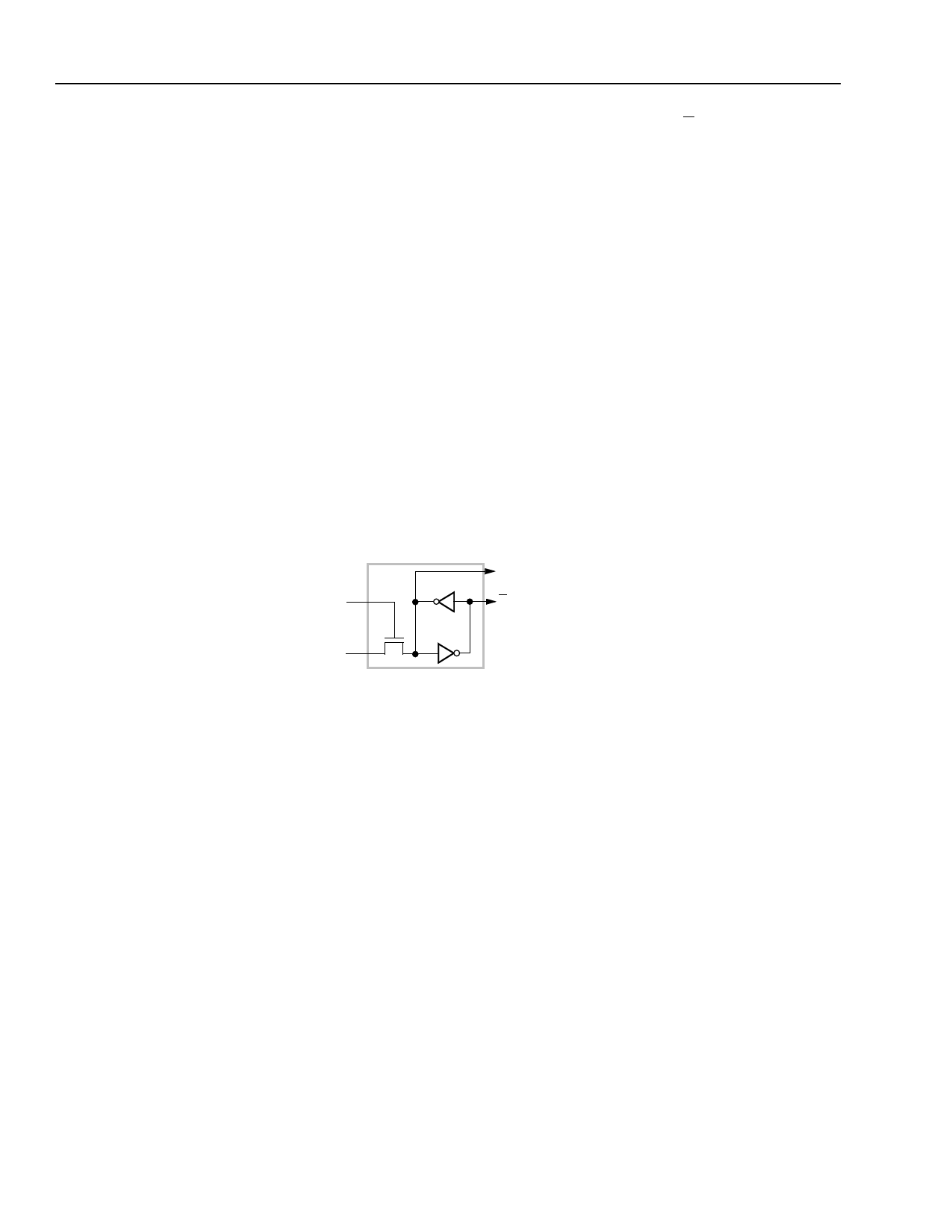

As shown in Figure 2, the basic memory cell consists of

two CMOS inverters plus a pass transistor used for

writing and reading cell data. The cell is only written to

during configuration and only read from during read-

back. During normal operation, the cell provides contin-

uous control and the pass transistor is off and does not

affect cell stability. This is quite different from the opera-

tion of conventional memory devices, in which the cells

are frequently read and rewritten.

The memory cell outputs Q and Q use full ground and

VCC levels and provide continuous, direct control. The

additional capacitive load and the absence of address

decoding and sense amplifiers provide high stability to

the cell. Due to their structure, the configuration mem-

ory cells are not affected by extreme power supply

excursions or very high levels of alpha particle radia-

tion. Soft errors have not been observed in reliability

testing.

Two methods of loading configuration data use serial

data, while three use byte-wide data. The internal con-

figuration logic utilizes framing information, embedded

in the program data by the ORCA Foundry Develop-

ment System, to direct memory cell loading. The serial

data framing and length count preamble provide pro-

gramming compatibility for mixes of various Lucent pro-

grammable gate arrays in a synchronous, serial, daisy-

chain fashion.

READ OR

WRITE

Q CONFIGURATION

CONTROL

Q

DATA

5-3101(F)

Figure 2. Static Configuration Memory Cell

4

Lucent Technologies Inc.