LV1100 Ver la hoja de datos (PDF) - SANYO -> Panasonic

Número de pieza

componentes Descripción

Fabricante

LV1100 Datasheet PDF : 10 Pages

| |||

LV1100

Delay Time Data (D6 to D8)

D6

D7

D8

CLK FAST

CLK SLOW

L

L

L

10 ms

20 ms

L

L

H

20 ms

40 ms

L

H

L

30 ms

60 ms

L

H

H

40 ms

80 ms

H

L

L

50 ms

100 ms

H

L

H

60 ms

120 ms

Note: D6, D7, and D8 must not be used for any purposes other than the above commands.

L

D9

SYSTEM MUTE ON

D10

CLK FAST

Control Data Format

H

SYSTEM MUTE OFF

CLK SLOW

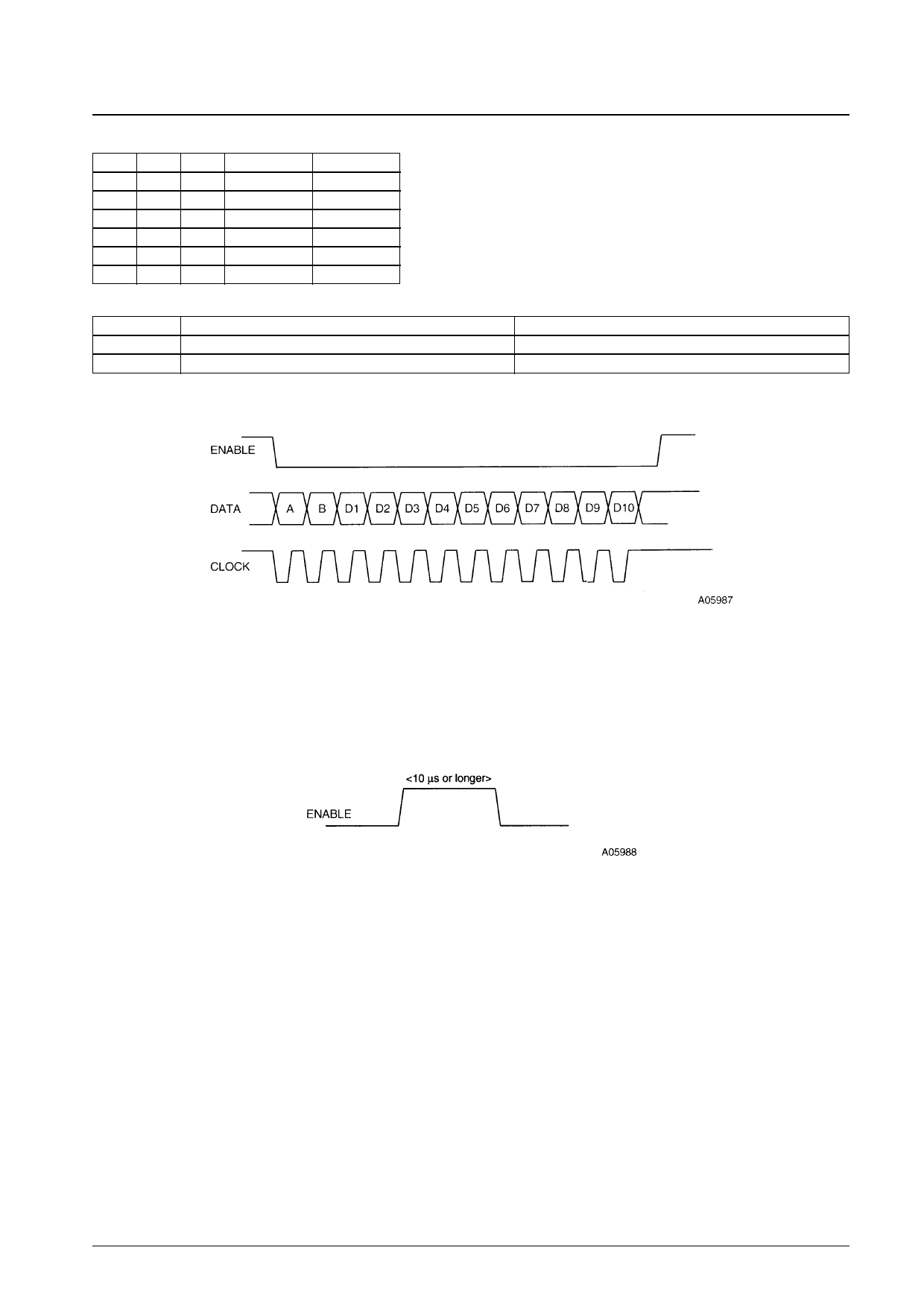

• Data is read in on the rising edge of the clock.

• The control data consists of 12 bits.

• The input data is latched on the rising edge of the enable signal.

• The clock and enable signals must be held high when not being used to control the LV1100.

• Command interval time

The timing of intervals between enable signals must meet the conditions shown in the figure.

Notes on Mode Control (System Mute Usage)

1 When power is first applied, after the IC is fully operating (about 2 seconds after power is applied) applications must

send commands that turn the system muting off and then on again.

2 Applications must perform system muting on/off operations when switching the delay time or clock fast/slow

settings. After sending a system muting on command along with the new data, send the new data again, this time with

a system muting off command.

Note: By performing the operations described in items 1 and 2 here, the memory contents are initialized, thus preventing incorrect operation.

No. 5506-6/10