WED3C7410E16M-400BX Ver la hoja de datos (PDF) - White Electronic Designs Corporation

Número de pieza

componentes Descripción

Fabricante

WED3C7410E16M-400BX Datasheet PDF : 13 Pages

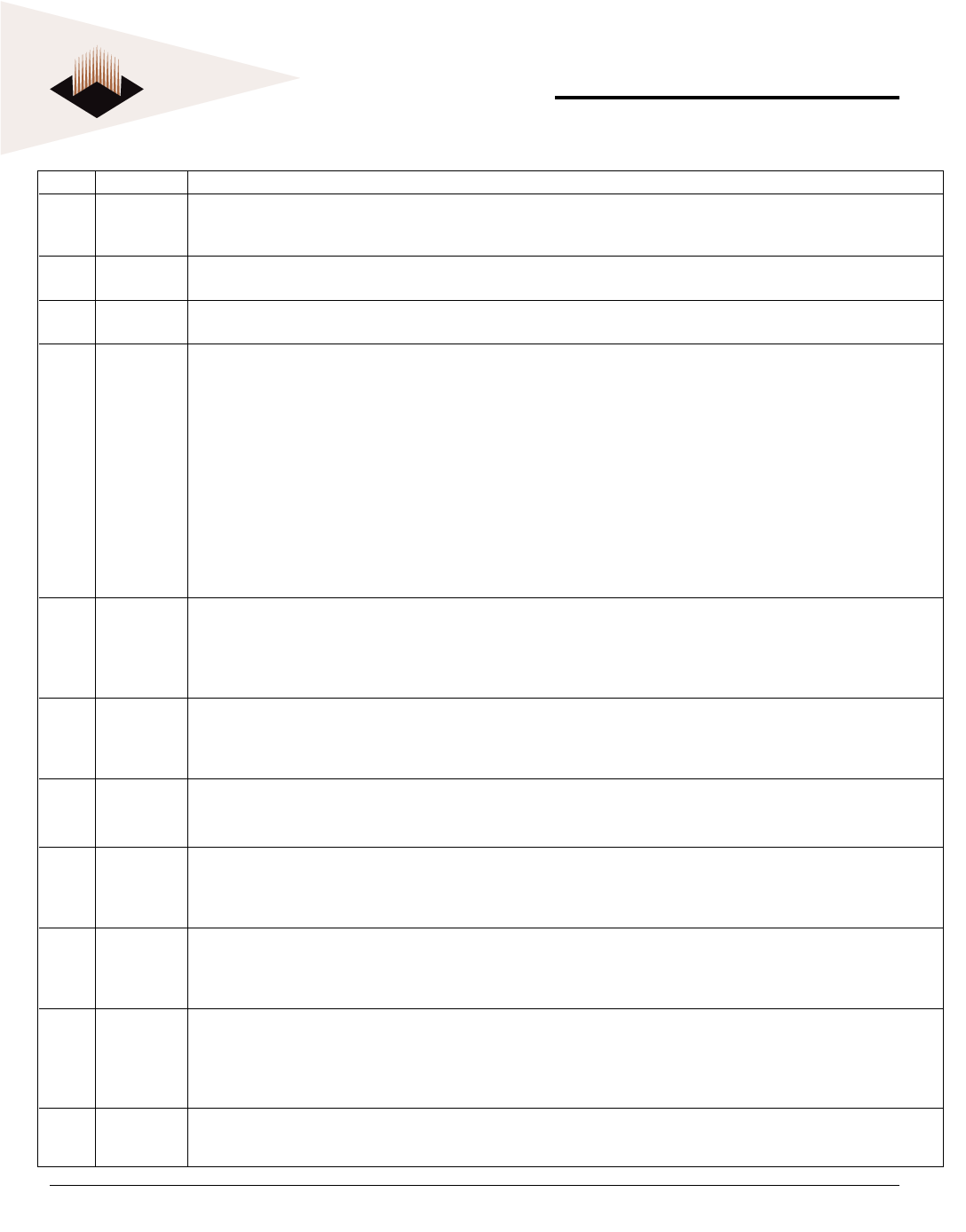

| |||

White Electronic Designs WED3C7410E16M-400BX

Bit

Name

0

L2E

1

L2PE

2–3

L2SIZ

4–6

L2CLK

7–8

L2RAM

9

L2DO

10

L2I

11

L2CTL

12

L2WT

13

L2TS

14–15

L2OH

TABLE 1: L2CR BIT SETTINGS

Function

L2 enable. Enables L2 cache operation (including snooping) starting with the next transaction the L2 cache unit receives. Before

enabling the L2 cache, the L2 clock must be configured through L2CR[2CLK], and the L2 DLL must stabilize. All other L2CR bits must

be set appropriately. The L2 cache may need to be invalidated globally.

L2 data parity checking enable. Enables parity generation and checking for the L2 data RAM interface. When disabled, generated

parity is always zeros. L2 Parity is supported by WEDC’s WED3C7410E16M-400BX, but is dependent on application.

L2 size—Should be set according to the size of the private memory setting. Total SRAM space is 2M bytes (256Kx72). See L2

cache/private memory configurations table in Motorola User’s Manual.

L2 clock ratio (core-to-L2 frequency divider). Specifies the clock divider ratio based from the core clock frequency that the

L2 data RAM interface is to operate at. When these bits are cleared, the L2 clock is stopped and the on-chip DLL for the L2

interface is disabled. For nonzero values, the processor generates the L2 clock and the on-chip DLL is enabled. After the L2 clock

ratio is chosen, the DLL must stabilize before the L2 interface can be enabled. The resulting L2 clock frequency cannot be slower

than the clock frequency of the 60x bus interface.

000 L2 clock and DLL disabled

001 ÷ 1

010 ÷ 1.5

011 ÷ 3.5

100 ÷ 2

101 ÷ 2.5

110 ÷ 3

111 ÷ 4

L2 RAM type—Configures the L2 RAM interface for the type of synchronous SRAMs used:

• Pipelined (register-register) synchronous burst SRAMs that clock addresses in and clock data out

The 7410 does not burst data into the L2 cache, it generates an address for each access.

10: Pipelined (register-register) synchronous burst SRAM - Setting for WED3C7410E16M-400BX

L2 data only. Setting this bit enablesÚdata-only operation in the L2 cache. When this bit is set, only transactions from the L1 data

cache can be cached in the L2 cache. L1 instruction cache operations will be serviced for instruction addresses already in the L2

cache; however, the L2 cache will not be reloaded for L1 instruction cache misses. Note that setting both L2DO and L2IO effectively

locks the L2 cache.

L2 global invalidate. Setting L2I invalidates the L2 cache globally by clearing the L2 status bits. This bit must not be set while the L2

cache is enabled. See

Motorola’s User manual for L2 Invalidation procedure.

L2 RAM control (ZZ enable). Setting L2CTL enables the automatic operation of the L2ZZ (low-power mode) signal for cache RAMs.

Sleep mode is supported by the WED3C7410E16M-400BX. While L2CTL is asserted, L2ZZ asserts automatically when the device

enters nap or sleep mode and negates automatically when the device exits nap or sleep mode. This bit should not be set when the

device is in nap mode and snooping is to be performed through deassertion of QACK.

L2 write-through. Setting L2WT selects write-through mode (rather than the default write-back mode) so all writes to the L2 cache also

write through to the system bus. For these writes, the L2 cache entry is always marked as clean (value unmodified) rather than dirty

(value modified). This bit must never be asserted after the L2 cache has been enabled as previously-modified lines can get remarked

as clean (value unmodified) during normal operation.

L2 test support. Setting L2TS causes cache block pushes from the L1 data cache that result from dcbf and dcbst instructions to be

written only into the L2 cache and marked valid, rather than being written only to the system bus and marked invalid in the L2 cache

in case of hit. This bit allows a dcbz/dcbf instruction sequence to be used with the L1 cache enabled to easily initialize the L2 cache

with any address and data information. This bit also keeps dcbz instructions from being broadcast on the system and single-beat

cacheable store misses in the L2 from being written to the system bus.

L2 output hold. These bits configure output hold time for address, data, and control signals driven to the L2 data RAMs.

01: 0.8ns Hold Time - Setting for WED3C7410E16M-400BX

9

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com