UDN2917 Ver la hoja de datos (PDF) - Allegro MicroSystems

Número de pieza

componentes Descripción

Fabricante

UDN2917 Datasheet PDF : 8 Pages

| |||

2917

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

CURRENT-CONTROL

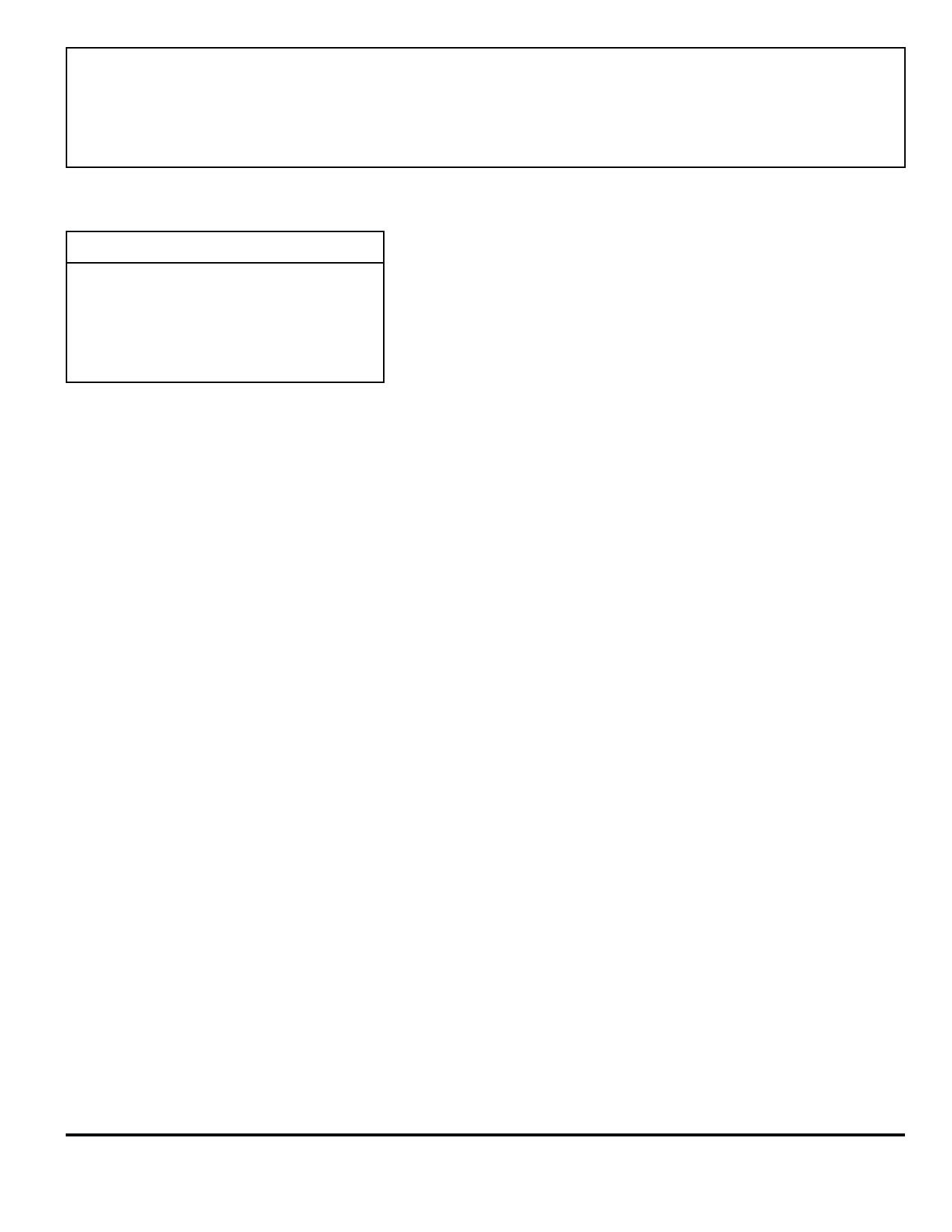

TRUTH TABLE

I0

I1

Output Current

L

L

VREF/10 RS = ITRIP

H

L

VREF /15 RS = 2/3 ITRIP

L

H

VREF /30 RS = 1/3 ITRIP

H

H

0

Loads with high distributed capacitances may result in high turn-on

current peaks. This peak (appearing across RS) will attempt to trip the

comparator, resulting in erroneous current control or high-frequency

oscillations. An external RCCC low-pass filter may be needed to delay

the action of the comparator.

LOGIC CONTROL OF OUTPUT CURRENT

Two logic level inputs (I0 and I1) allow digital selection of the motor

winding current at 100%, 67%, 33%, or 0% of the maximum level per

the table. The 0% output current condition turns off all drivers in the

bridge and can be used as an output enable function. These logic level

inputs greatly enhance the implementation of µP-controlled drive

formats.

During half-step operations, the I0 and I1 inputs allow the µP to

control the motor at a constant torque between all positions in an eight-

step sequence. This is accomplished by digitally selecting 100% drive

current when only one phase is on and 67% drive current when two

phases are on.

The logic control inputs can also be used to select a reduced

current level (and reduced power dissipation) for ‘hold’ conditions

and/or increased current (and available torque) for start-up conditions.

GENERAL

To avoid excessive voltage spikes on the LOAD SUPPLY pin

(VBB), a large-value capacitor (≥47 µF) should be connected from VBB

to ground as close as possible to the device. Under no circumstances

should the voltage at LOAD SUPPLY exceed 45 V.

The PHASE input to each bridge determines the direction motor

winding current flows. An internally generated deadtime (approxi-

mately 3 µs) prevents crossover currents that can occur when switch-

ing the PHASE input.

All four drivers in the bridge output can be turned off (VEN ≥ 2.4 V

or I0 = I1 ≥ 2.4 V), resulting in a fast current decay through the internal

output clamp and flyback diodes. The fast current decay is desirable

in half-step and high-speed applications. All logic inputs float high; the

ENABLE input must be tied low if it is not used.

Varying the reference voltage (VREF) provides continuous control

of the peak load current for micro-stepping applications, within the

specified limits for VREF.

Thermal protection circuitry turns off all drivers when the junction

temperature reaches +170°C. It is only intended to protect the device

from failures due to excessive junction temperature and should not

imply that output short circuits are permitted. The output drivers are

re-enabled when the junction temperature cools to +145°C.

www.allegromicro.com