IDT723614L30PQF Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Fabricante

IDT723614L30PQF

IDT723614L30PQF Datasheet PDF : 39 Pages

| |||

IDT723614 CMOS SyncBiFIFO™ WITH BUS MATCHING AND BYTE SWAPPING

64 x 36 x 2

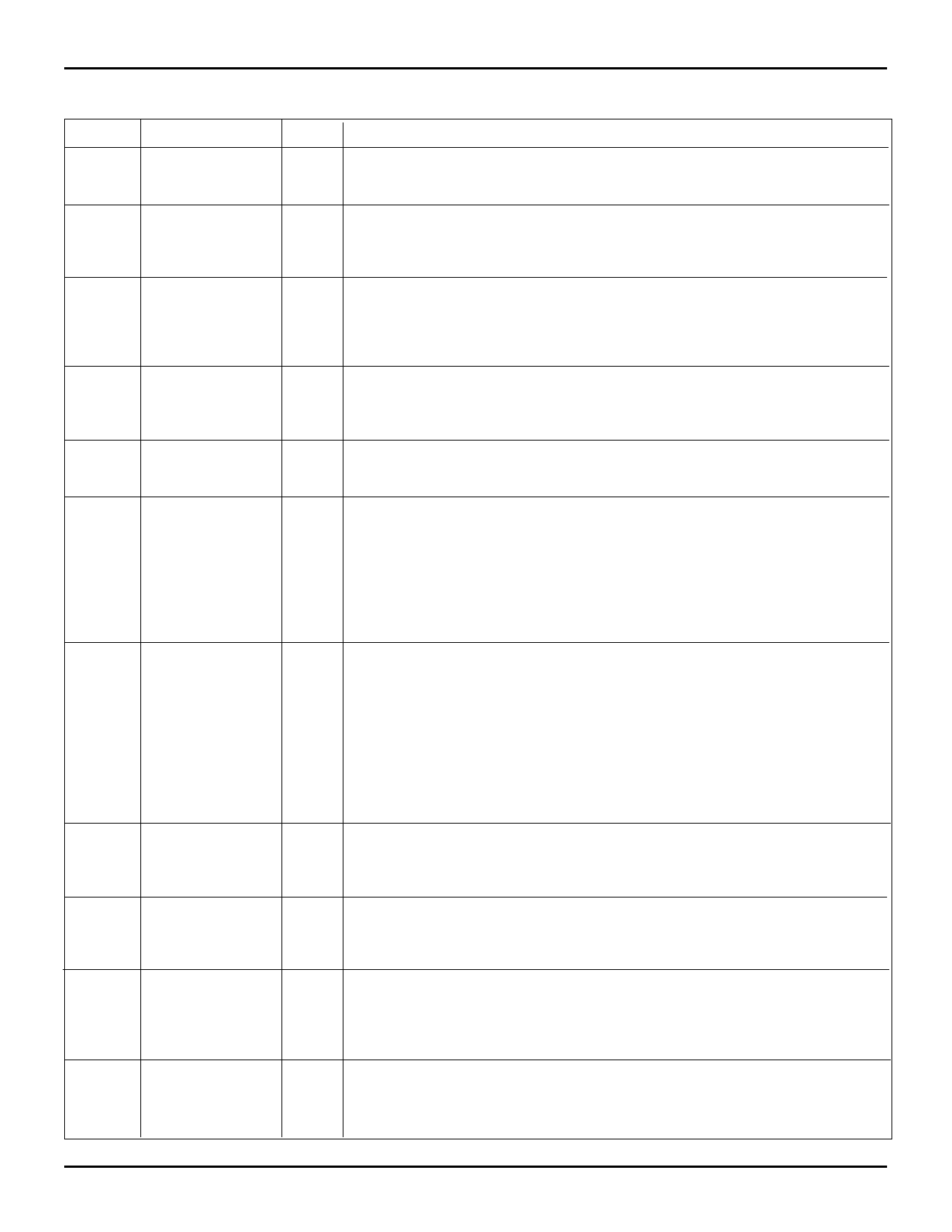

PIN DESCRIPTION (CONTINUED)

COMMERCIAL TEMPERATURE RANGE

Symbol

Name

`FS1, FS0 Flag-Offset Selects

I/O

Description

I The LOW-to-HIGH transition of RST latches the values of FS0 and FS1, which

selects one of four preset values for the almost-full flag and almost-empty flag

offset.

MBA

MBF1

MBF2

ODD/

EVEN

PEFA

Port A Mailbox

I A HIGH level on MBA chooses a mailbox register for a port A read or write

Select

operation. When the A0-A35 outputs are active, a HIGH level on MBA selects

data from the mail2 register for output, and a LOW level selects FIFO2 output

register data for output.

Mail1 Register Flag

O MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to the

mail1 register. Writes to the mail1 register are inhibited while MBF1 is set LOW.

MBF1 is set HIGH by a LOW-to-HIGH transition of CLKB when a port B read is

selected and both SIZ1 and SIZ0 are HIGH. MBF1 is set HIGH when the device

is reset.

Mail2 Register Flag

O MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the

mail2 register. Writes to the mail2 register are inhibited while MBF2 is set LOW.

MBF2 is set HIGH by a LOW-to-HIGH transition of CLKA when a port A read is

selected and MBA is HIGH. MBF2 is set HIGH when the device is reset.

Odd/Even Parity

Select

I Odd parity is checked on each port when ODD/EVEN is HIGH, and even parity is

checked when ODD/EVEN is LOW. ODD/EVEN also selects the type of parity

generated for each port if parity generation is enabled for a readoperation.

Port A Parity Error

O When any byte applied to terminals A0-A35 fails parity, PEFA is LOW. Bytes are

Flag

(Port A) organized as A0-A8, A9-A17, A18-A26, and A27-A35, with the most significant

bit of each byte serving as the parity bit. The type of parity checked is deter

mined by the state of the ODD/EVEN input.

PEFB

Port B Parity Error

Flag

The parity trees used to check the A0-A35 inputs are shared by the mail2 register

to generate parity if parity generation is selected by PGA. Therefore, if a mail2

read parity generation is setup by having W/RA LOW, MBA HIGH, and PGA

HIGH, the PEFA flag is forced HIGH regardless of the A0-A35 inputs.

O When any valid byte applied to terminals B0-B35 fails parity, PEFB is LOW. Bytes

(Port B) are organized as B0-B8, B9-B17, B18-B26, B27-B35 with the most significant bit

of each byte serving as the parity bit. A byte is valid when it is used by the bus

size selected for Port B. The type of parity checked is determined by the state of

the ODD/EVEN input.

The parity trees used to check the B0-B35 inputs are sharedby the mail 1 register to

generate parity if parity generation isselected by PGB. Therefore, if a mail1 read

with parity generation is setup by having W/RB LOW, SIZ1 and SIZ0 HIGH, and

PGB HIGH, the PEFB flag is forced HIGH regardless of the state of the B0-B35

inputs.

PGA

Port A Parity

Generation

I Parity is generated for data reads from port A when PGA is HIGH. The type of

parity generated is selected by the state of the ODD/EVEN input. Bytes are

organized as A0-A8, A9-A17, A18-A26, and A27-A35. The generated parity

bits are output in the most significant bit of each byte.

PGB

Port B Parity

Generation

RST Reset

SIZ0, SIZ1 Port B bus size

selects

I Parity is generated for data reads from port B when PGB is HIGH. The type

of parity generated is selected by the state of the ODD/EVEN input. Bytes are

organized as B0-B8, B9-B17, B18-B26, and B27-B35. The generated parity

bits are output in the most significant bit of each byte.

I To reset the device, four LOW-to-HIGH transitions of CLKA and four LOW-to-

HIGH transitions of CLKB must occur while RST is LOW. This sets the AFA,

AFB, MBF1, and MBF2 flags HIGH and the EFA, EFB, AEA, AEB, FFA, and

FFB flags LOW. The LOW-to-HIGH transition of RST latches the status of the

FS1 and FS0 inputs to select almost-full and almost-empty flag offsets

I A LOW-to-HIGH transition of CLKB latches the states of SIZ0, SIZ1, and BE, and

(Port B) the following LOW-to-HIGH transition of CLKB implements the latched states as a

port B bus size. Port B bus sizes can be long word, word, or byte. A high on both

SIZ0 and SIZ1 accesses the mailbox reegisters for a port B 36-bit write or read.

5