IDT723632L15PFG(2015) Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Fabricante

IDT723632L15PFG

(Rev.:2015)

(Rev.:2015)

IDT723632L15PFG Datasheet PDF : 24 Pages

| |||

IDT723622/723632/723642 CMOS SyncBiFIFO™

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

pointer comparator that indicates when the FlFO memory status is full,

full-1, or full-2. From the time a word is read from a FIFO, its previous

memory location is ready to be written in a minimum of two cycles of the

Input Ready flag synchronizing clock. Therefore, an Input Ready flag is

LOW if less than two cycles of the Input Ready flag synchronizing clock

have elapsed since the next memory write location has been read. The

second LOW-to-HIGH transition on the Input Ready flag synchronizing

Clock after the read sets the Input Ready flag HIGH.

A LOW-to-HIGH transition on an Input Ready flag synchronizing

clock begins the first synchronization cycle of a read if the clock transition

occurs at time tSKEW1 or greater after the read. Otherwise, the subsequent

clock cycle can be the first synchronization cycle (see Figures 10 and 11

for timing diagrams).

ALMOST-EMPTY FLAGS (AEA, AEB)

The Almost-Empty flag of a FIFO is synchronized to the port clock that reads

data from its array. The state machine that controls an Almost-Empty flag monitors

a write pointer and read pointer comparator that indicates when the FIFO

memory status is almost-empty, almost-empty+1, or almost-empty+2. The

almost-empty state is defined by the contents of register X1 for AEB and

register X2 for AEA. These registers are loaded with preset values during

a FIFO reset or programmed from port A (see Almost-Empty flag and

Almost-Full flag offset programming section). An Almost-Empty flag is

LOW when its FIFO contains X or less words and is HIGH when its FIFO

contains (X+1) or more words. A data word present in the FIFO output

register has been read from memory.

Two LOW-to-HIGH transitions of the Almost-Empty flag synchronizing

clock are required after a FIFO write for its Almost-Empty flag to reflect the new

level of fill. Therefore, the Almost-Full flag of a FIFO containing (X+1) or more

words remains LOW if two cycles of its synchronizing clock have not elapsed

since the write that filled the memory to the (X+1) level. An Almost-Empty flag

is set HIGH by the second LOW-to-HIGH transition of its synchronizing clock after

the FIFO write that fills memory to the (X+1) level. A LOW-to-HIGH transition of

an Almost-Empty flag synchronizing clock begins the first synchronization cycle

if it occurs at time tSKEW2 or greater after the write that fills the FIFO to (X+1) words.

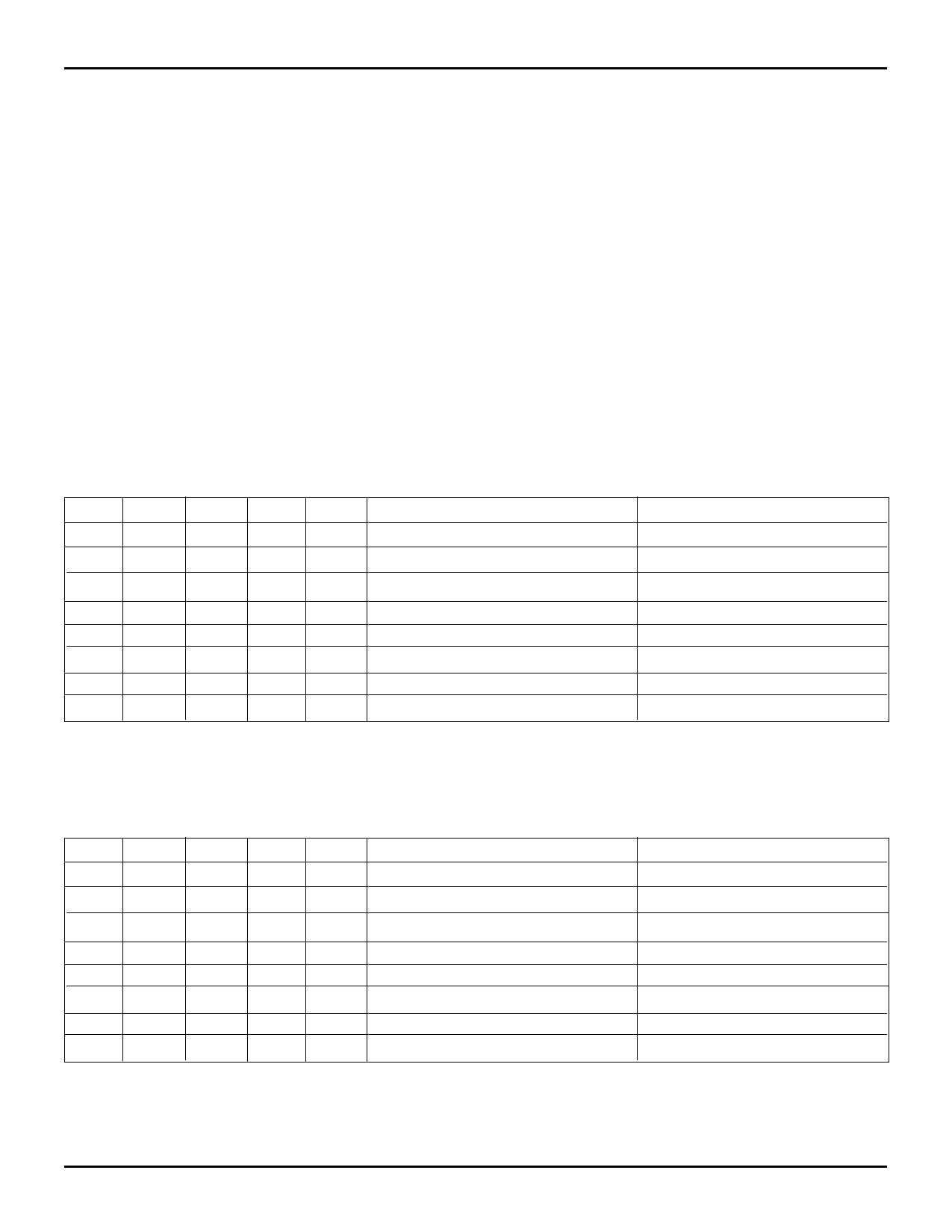

TABLE 4 — FIFO1 FLAG OPERATION

IDT723622(3)

0

Number of Words in FIFO(1,2)

IDT723632(3)

0

IDT723642(3)

0

Synchronized

to CLKB

ORB

AEB

L

L

Synchronized

to CLKA

AFA

IRA

H

H

1 to X1

1 to X1

1 to X1

H

L

H

H

(X1+1) to [256-(Y1+1)]

(X1+1) to [512-(Y1+1)]

(X1+1) to [1,024-(Y1+1)]

H

H

H

H

(256-Y1) to 255

(512-Y1) to 511

(1,024-Y1) to 1,023

H

H

L

H

256

512

1,024

H

H

L

L

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X1 is the Almost-Empty offset for FIFO1 used by AEB. Y1 is the Almost-Full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a reset of FIFO1 or

programmed from port A.

TABLE 5 — FIFO2 FLAG OPERATION

IDT723622(3)

0

Number of Words in FIFO(1,2)

IDT723632(3)

0

IDT723642(3)

0

Synchronized

to CLKA

ORA

AEA

L

L

Synchronized

to CLKB

AFB

IRB

H

H

1 to X2

1 to X2

1 to X2

H

L

H

H

(X2+1) to [256-(Y2+1)]

(X2+1) to [512-(Y2+1)]

(X2+1) to [1,024-(Y2+1)]

H

H

H

H

(256-Y2) to 255

(512-Y2) to 511

(1,024-Y2) to 1,023

H

H

L

H

256

512

1,024

H

H

L

L

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X2 is the Almost-Empty offset for FIFO2 used by AEA. Y2 is the Almost-Full offset for FIFO2 used by AFB. Both X2 and Y2 are selected during a reset of FIFO2 or

programmed from port A.

11